Sundance Multiprocessor Technology Limited

| Module Description:   | PC/104 OneBank Dual-DSP + FPGA w. FMC Module |

|-----------------------|----------------------------------------------|

| Module Number:        | SMT6657                                      |

| Current Issue Number: | 1.4                                          |

| Original Issue Date:  | 29 <sup>th</sup> November 2015               |

| Original Author:      | S E Carpenter                                |

# PCIe/104<sup>™</sup> OneBank Dual TI TMS320C6657 + Kintex-7 KU35 + VITA57.1 FMC Module

# **Design Description**

# Part #: SMT 6657

Sundance Multiprocessor Technology Ltd, Chiltern House, Waterside, Chesham, Bucks. HP5 1PS. This document is the property of Sundance and may not be copied nor communicated to a third party without prior written permission. © Sundance Multiprocessor Technology Limited 2016

Certificate Number FM55022

Issue 1.4

# **Revision History**

| Issue | Changes Made                                                                                                                                                                                                                                                                                                                                                                            | Date                         | Initials |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------|

| 0.1   | First Sundance unofficial draft.                                                                                                                                                                                                                                                                                                                                                        | 21SEP15                      | SEC      |

| 0.2   | Additional edits                                                                                                                                                                                                                                                                                                                                                                        | 22SEP15                      | FC       |

| 0.3   | Added 8 x MGT and 8 x FPGA I/O to the down<br>connector, 1 x MGT to FMC connector, SMBUS to I2C<br>BUS Router. Rerouted DSPA SPI port to FMC<br>through DSP FPGA. Change DSP power sequence to<br>tabular state machine.                                                                                                                                                                | 22SEP15                      | SEC      |

| 0.4   | Change to 4 x MGT to the down connector, 8 MGT to the FMC connector                                                                                                                                                                                                                                                                                                                     | 23SEP15                      | SEC      |

| 1.0   | First release.                                                                                                                                                                                                                                                                                                                                                                          | 25SEP15                      | SEC      |

| 1.1   | Revised FPGA pin allocation, added -40°C to +100°C contact Sundance, replaced pcie/104 reset to fpga with reset from cpld, updated block diagram.                                                                                                                                                                                                                                       | 230CT15                      | SEC      |

| 1.2   | Corrected FPGA pin allocation table (FMC)<br>Watchdog moved from CPLD to FPGA to allow<br>programming. Dedicated watchdog signal from<br>FPGA to CPLD added. GPIO8 changed from<br>watchdog to FPGA_PROGRAM_B configuration<br>control. CPLD STATUS_DATA & STATUS_CLOCK<br>replace DIPSWDAT and DIPSWCLK, and data<br>includes FPGA configuration status. Added I2C bus<br>address map. | 21DEC15                      | SEC      |

| 1.3   | Moved SMBUS to I2C router inside FPGA to save pcb space. Reduced FPE general I/O from 8 to 4. Added FPE pin allocation.                                                                                                                                                                                                                                                                 | 14MAR16                      | SEC      |

| 1.4   | Added PCB build information and fully routed board image.                                                                                                                                                                                                                                                                                                                               | 25 <sup>th</sup> May<br>2016 | GKP      |

# **Table of Contents**

| 1 | Introduction                                       | 5  |

|---|----------------------------------------------------|----|

|   | 1.1 Main Features                                  | 5  |

|   | 1.1.1 Hardware                                     | 5  |

|   | 1.1.2 Standards-based external interfaces          | 5  |

|   | 1.1.3 Interconnection between programmable devices | 7  |

|   | 1.1.4 TI comport compatibility                     | 7  |

| 2 | Notes                                              | 8  |

|   | 2.1 Abbreviations / Definitions                    | 8  |

|   | 2.2 Sundance References                            | 8  |

|   | 2.3 Internet References                            | 8  |

| 3 | System Architecture                                | 10 |

|   | 3.1 Block Diagram                                  | 11 |

|   | 3.2 FMC Data Acquisition Interface                 |    |

|   | 3.3 PCIe/104 Interface                             | 12 |

|   | 3.4 FPGA Interfaces                                |    |

|   | 3.4.1 FPGA POWER                                   |    |

|   | 3.4.2 FPGA EMIF16                                  |    |

|   | 3.4.3 FPGA SRIO                                    |    |

|   | 3.4.4 FPGA UART                                    |    |

|   | 3.4.5 FPGA DSP GPIO                                |    |

|   | 3.4.6 FPGA PCIe                                    |    |

|   | 3.4.7 FPGA MGT to Carrier Board                    |    |

|   | 3.4.8 FPGA General I/O to Carrier Board            |    |

|   | 3.4.9 FPGA PWRGOOD & ALERT                         |    |

|   | 3.4.10FPGA I2C                                     |    |

|   | 3.4.11FPGA SPI                                     |    |

|   | 3.4.12FPGA I/O LVDS                                |    |

|   | 3.4.13FPGA I/O LEDS.                               |    |

|   | 3.4.14FPGA I/O LVTTL                               |    |

|   | 3.4.15FPGA I/O & FMC JTAG                          |    |

|   | 3.4.16FPGA LOCAL LEDS                              |    |

|   | 3.4.17FPGA FMC LVDS CLOCKS                         |    |

|   | 3.4.18FPGA FMC DATA I/O LA00-33                    |    |

|   | 3.4.19FPGA FMC SPI<br>3.4.20FPGA FMC INTERRUPTS    |    |

|   |                                                    |    |

|   | 3.4.21FPGA FMC MGT<br>3.5 DSP Interfaces           |    |

|   | 3.5 DSP Interfaces                                 |    |

|   | 3.5.2 DSP JTAG                                     |    |

|   | 3.5.3 DSP EMIF16                                   |    |

|   | 3.5.4 DSP UART                                     |    |

|   | J.J.F DOI UANI                                     |    |

| 3.5.5 DSP GPIO                                 | 32 |

|------------------------------------------------|----|

| 3.5.6 DSP RESET                                | 33 |

| 3.5.7 DSP POWER                                | 33 |

| 3.5.8 DSP SRIO                                 | 35 |

| 3.5.9 DSP HYPERLINK                            | 35 |

| 3.5.10DSP PCIe                                 | 35 |

| 3.5.11DSP EMIF32 & DDR3 memory                 | 36 |

| 3.5.12DSP I2C                                  | 37 |

| 3.6 I2C Temperature Sensor                     | 38 |

| 3.7 I2C Supply Volts ADC                       | 39 |

| 3.8 CPLD                                       | 40 |

| 3.9 DSP Booting                                | 43 |

| 3.9.1 DIP Switches                             | 44 |

| 3.10 Flash Memories                            |    |

| 3.10.1256KByte I <sup>2</sup> C EEPROM         | 45 |

| 3.10.2256MByte Parallel NOR Flash              | 45 |

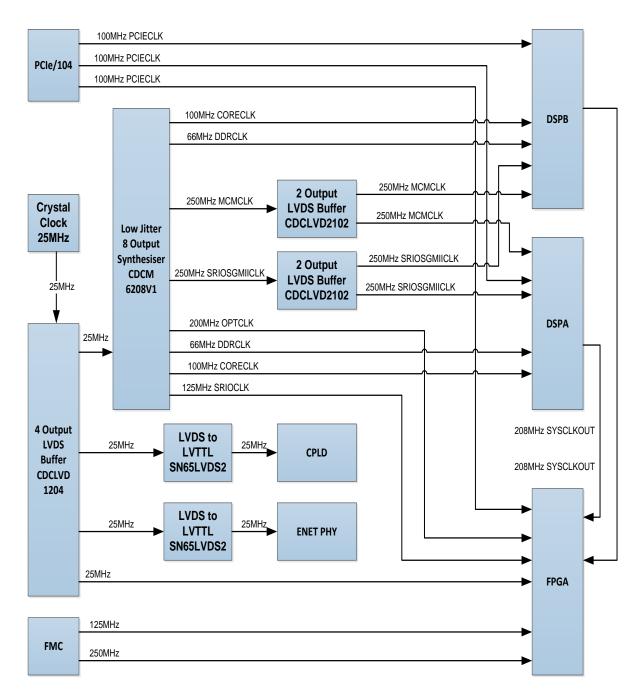

| 3.11 Clock System                              | 47 |

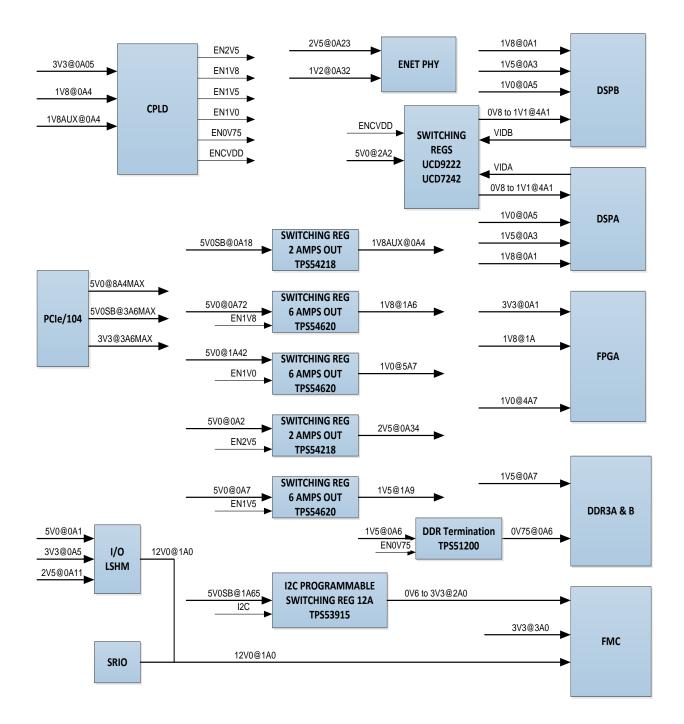

| 3.12 Power Supplies                            | 51 |

| 3.13 I/O expansion connector                   | 55 |

| 3.14 SRIO expansion connector                  | 57 |

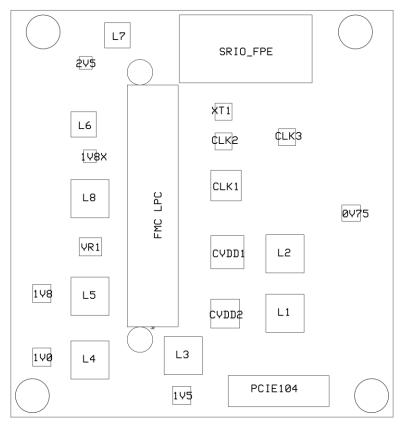

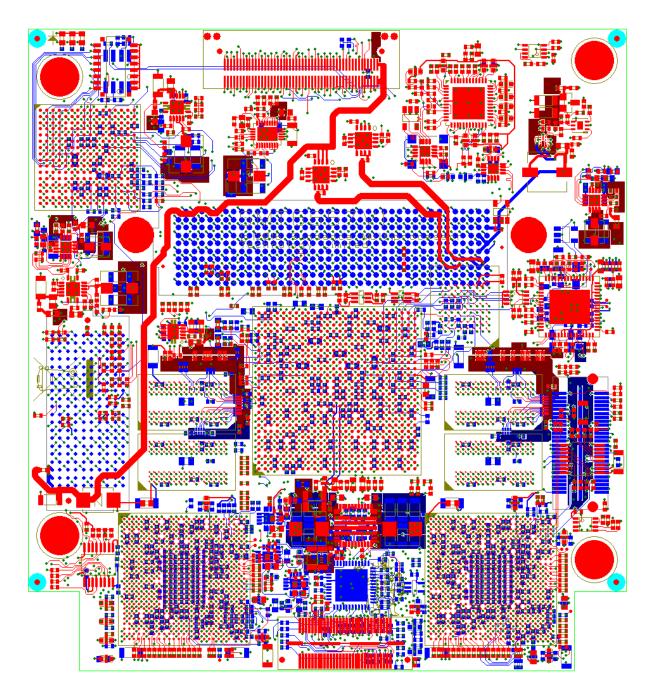

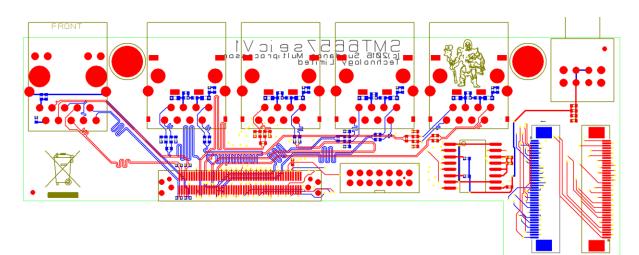

| 4 PCB Layout                                   | 59 |

| 4.1 Heat Sinks                                 | 59 |

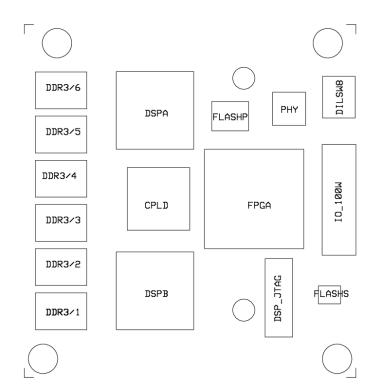

| 4.2 Component Placement                        | 59 |

| 4.3 PCB Construction                           | 61 |

| 4.4 PCB Layout                                 | 64 |

| 4.4.1 Main Board                               |    |

| 4.4.2 Front Panel Interface Board              | 65 |

| 5 Physical Properties                          | 66 |

| 6 Verification, Review & Validation Procedures | 67 |

| 7 Safety                                       | 67 |

| 8 EMC Statement of Compliance                  | 67 |

| 9 Ordering Information                         | 67 |

# 1 Introduction

This document is the design description of a dual DSP+FPGA PCIe/104 module, which describes the hardware design in detail. Where possible specific devices are identified for use in the design, along with how they are connected.

This document provides a set of design requirements, which are used by the PCB designer, and for PCB testing.

The SMT6657 dual-DSP+FPGA module is a reliable and flexible platform for digital signal processing applications requiring high-performance integer and floating-point computation.

It is applicable to both symmetric multiprocessing applications in which the computational load is shared by the two DSPs; and asymmetric applications where one of the DSPs is responsible for hard real-time processing and the other acts as a supervisor, handling all non-deterministic communication and optionally running under control of an operating system.

#### 1.1 Main Features

#### 1.1.1 Hardware

This module consists of the following major hardware features:

- 1) PCIe/104<sup>™</sup> OneBank plug-able module format

- 2) Two dual-core <u>TI</u> C6657 floating-point DSPs

- 3) Xilinx <u>Kintex-7 Ultra Scale</u> series FPGA

- 4) Serial RapidIO and Hyperlink connectivity between DSPs

- 5) Accepts one <u>FMC-LPC<sup>™</sup></u> Mezzanine Card data acquisition add-on module

- 6) Additional stack-down SRIO connector to SMT-Carrier-GSI

- 7) Front panel I/O connector carrying gigabit Ethernet and flexible FPGA I/O

#### 1.1.2 Standards-based external interfaces

The SMT-DSP-GSI module benefits from the incorporation of three key interface standards, each one the leading standard in its area of the embedded systems field:

- 1) PCIe/104<sup>™</sup> provides tightly integrated high-speed connectivity with PC hosts and also defines a compact and rugged module format.

- 2) FMC provides an FPGA-oriented data acquisition card interface that is particularly well suited to analogue conversion applications. Due to the flexibility of FPGA I/O, the function of its 68 pins (Low pin count FMC; or 160 pins for the High Pin Count version) can optimised to the needs of the FMC add-on module.

- 3) Serial RapidIO is a standard designed to address the need for inter-module communication in high bandwidth embedded systems such as 4G wireless base stations, and has become a standard peripheral in high-end TI DSPs.

# 1.1.3 Interconnection between programmable devices

#### Carrier to DSPs

- One 500MByte/s PCIe Gen2 lane to each DSP, for memory-mapped host communication

- One 500MByte/s PCIe Gen2 lane to the FPGA

- Two 500MByte/s SRIO lanes to each DSP, for telegram-oriented communication between DSP modules

- Four 500MByte/s PCIe Gen2 lanes to the FPGA

#### DSP to DSP

- 4GByte/s TI Hyperlink for memory-sharing between DSPs

- One 500MByte/s SRIO lane between DSPs, for telegram-oriented communication between DSPs

#### DSP to FPGA

- Each DSP has its own 100MByte/s 16-bit memory bus interface to the FPGA (also configurable as a Universal Parallel Port)

- Each DSP has one 500MByte/s SRIO lane to the FPGA

- All DSP GPIO is routed to the FPGA

- A full duplex 6MByte/s SPI communications channel for control and diagnostics

#### FPGA to FMC

- 34 user-definable I/O pairs, configurable to the interfacing needs of the FMC Data Acquisition card: ADC & DAC data, SPI bus, Interrupt

- Eight MGT 500MByte/s transceiver data pair

- Two clock signals

#### System Management Bus

• All I<sup>2</sup>C-capable devices including both DSPs, are connected to a single I<sup>2</sup>C bus, which extends to the I<sup>2</sup>C pins of the FMC connector and the SMbus pins of the PCIe/104<sup>™</sup> stack-down connector, through an SMBUS router within the FPGA.

#### 1.1.4 TI comport compatibility

The SMT6657 is supplied with firmware that permits <u>TMS320C40</u> comports to be implemented on its external I/O and/or FMC daughterboard interfaces. As each DSP has a memory bus connected to the FPGA, this functionality is exposed to the DSP software via a memory-mapped interface that is very similar to the original TI hardware implementation of comports.

# 2 Notes

Several part numbers are described in the text. These are possible part numbers, and alternative devices may be designed in at a later date.

| 2.1              | Abbreviations / Definitions                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                                                                                                                                                                        |

| ADC              | Analog to Digital Converter.                                                                                                                                                           |

| DAC              | Digital to Analogue Converter                                                                                                                                                          |

| DDR & DDR3       | Dual Data Rate. An interface mechanism where data is transferred on both rising and falling clock edges. DDR3 memory is lower power and higher performance than its predecessor, DDR2. |

| DRAM             | Dynamic RAM.                                                                                                                                                                           |

| FPGA             | Field Programmable Gate Array.                                                                                                                                                         |

| GPIO             | General Purpose Input Output.                                                                                                                                                          |

| I <sup>2</sup> C | Inter-integrated Circuit. A two wire low speed serial interface.                                                                                                                       |

| MAC              | Media Access Control.                                                                                                                                                                  |

| Magnetics        | Commonly used to refer to the inductors and transformers within the Ethernet signalling to the RJ45 connector.                                                                         |

| PHY              | Commonly used to refer to the device that interfaces to the physical layer.                                                                                                            |

| RAM              | Random Access Memory.                                                                                                                                                                  |

| SEIC             | Sundance External Interface Connector, a module-specific breakout board for external I/O.                                                                                              |

| SPI              | Serial Peripheral Interface. A high speed serial interface.                                                                                                                            |

| SRIO             | Serial RapidIO (also known as Serial RocketIO). A multi-gigabit serial interface for peer-to-peer communication. Provides both message-passing and read/write transactions.            |

| EMIF32           | High speed synchronous 32 bit bus to the DDR3 SDRAM                                                                                                                                    |

| EMIF16           | Medium speed asynchronous 16 bit bus to the FPGA and flash ROM                                                                                                                         |

| SGMII            | 1G Ethernet interfaces to a dual 1G Ethernet PHY                                                                                                                                       |

| PCIE             | Dual lane gen 2                                                                                                                                                                        |

| JTAG             | Test and development connection to external emulation system                                                                                                                           |

| CLOCKS           | Multiple clocks to drive different parts of the DSP & FPGA                                                                                                                             |

| UART             | Standard asynchronous serial communications                                                                                                                                            |

| POWER            | Multiple power supplies for the core and the I/O                                                                                                                                       |

| MGT              | Multi Gigabit Transceiver                                                                                                                                                              |

| 2.2              | Sundance References                                                                                                                                                                    |

|                  |                                                                                                                                                                                        |

| [1]              | SMT-DSP-GSI (qcf51) v1_7.pdf                                                                                                                                                           |

| [2]              | SMT-FMC-GSI (qcf51) v1_5.pdf                                                                                                                                                           |

| [3]              | SMT-IO-GSI (qcf51) v1_4.pdf                                                                                                                                                            |

| [4]              | SMT-MBRD-GSI (qcf51) v1_5.pdf                                                                                                                                                          |

| 2.3              | Internet References                                                                                                                                                                    |

| 2.5              | Internet References                                                                                                                                                                    |

| [5]              | http://www.pc104.org/history.php                                                                                                                                                       |

| [6]              | http://shop.vita.com/ANSI-VITA-571-2008-R2010-FPGA-Mezzanine-Card-FMC-                                                                                                                 |

| r                | Standard-AV571.htm                                                                                                                                                                     |

| [7]              | http://www.ti.com/lsds/ti/dsp/keystone/overview.page                                                                                                                                   |

| [8]              | http://www.ti.com/lit/ug/sprugw1b/sprugw1b.pdf                                                                                                                                         |

| [9]  | http://www.xilinx.com/support/documentation/data_sheets/ds095.pdf                                  |

|------|----------------------------------------------------------------------------------------------------|

| [10] | http://www.ti.com/product/tms320c6657                                                              |

| [11] | http://www.xilinx.com/support/documentation/data_sheets/ds180_7Series_Overview.pdf                 |

| [12] | http://www.xilinx.com/support/documentation/data_sheets/ds182_Kintex_7_Data_Sh eet.pdf             |

| [13] | http://www.ti.com/tool/XDS560                                                                      |

| [14] | http://www.xilinx.com/support/documentation/data_sheets/ds593.pdf                                  |

| [15] | http://www.xilinx.com/support/documentation/data_sheets/ds892-kintex-ultrascale-<br>data-sheet.pdf |

| [16] | http://www.xilinx.com/products/technology/power/xpe.html                                           |

| [17] | http://www.xilinx.com/support/documentation/user_guides/ug570-ultrascale-<br>configuration.pdf     |

| [18] | http://www.ti.com/litv/pdf/spru655i                                                                |

| [19] | http://en.stackpc.org/specs.html                                                                   |

# 3 System Architecture

The DSP system consists of a PCIe/104 format PCB, with major components: A pair of 1.25GHz Texas Instruments DSPs part number: TMS320C6657CZH25 A Xilinx Kintex7 UltraScale FPGA part number: XCKU035-1FBVA676C.

These and all other components used are specified for operation in a laboratory environment over the temperature range of  $0^{\circ}$ C to  $+85^{\circ}$ C, and comply with ROHS requirements.

For operating requirements over the range of -40°C to +100°C, please contact Sundance.

The DSP PCB has thick copper power plane internal layers for high thermal and electrical conductivity. A solid aluminum heat sink provides further conduction cooling and rigidity and EMI shielding.

The system design around each DSP is largely symmetrical, apart from the boot procedure and non-deterministic interfaces.

DSP A is the master and boots first from the EMIF16 NOR FLASH PROM. Code running on DSP A is then responsible for booting DSP B and configuring the Kintex-7 FPGA.

With its large flash memory and gigabit Ethernet connection, DSP A is most suited to run a Real Time Operating System, leaving DSP B free to perform real time signal processing which is both deterministic and very low latency.

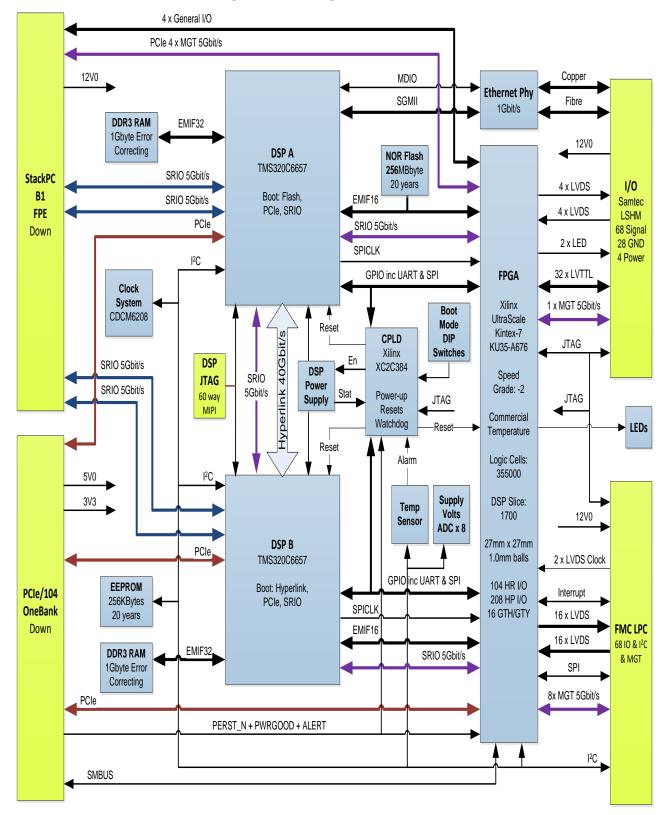

Below is a diagram showing the system architecture:

#### Figure 1 Block diagram of SMT6657

3.1

#### 3.2 FMC Data Acquisition Interface

The FMC is the "Low Pin Count" variant, which provides the following signals:

- 34 flexibly configured I/O pairs, which in the standard firmware are configured as

- 8 high speed LVDS double data rate inputs (for ADC sample data)

- 16 high speed LVDS outputs (for DAC sample data)

- SPI bus from the DSP FPGA

- Interrupt / DMA request to the DSP FPGA

- 2 LVDS data clocks

- I<sup>2</sup>C for peripheral configuration and status monitoring

- FPGA JTAG permitting debugging of the data acquisition module firmware

- Eight MGT 500MByte/s serial communications lanes

#### 3.3 PCIe/104 Interface

The PCIe/104 OneBank connector provides power, global Reset, PCI Express connections to the host, and I<sup>2</sup>C.

The first three PCIe lanes on the connector are routed to the two DSPs and the Kintex-7 FPGA. The SMT6657 board thus provides three separate PCIe x1 ports.

Each DSP has a single PCIe GEN2 port operating at up to 5G Baud per lane, which can be configured at reset as either a "Root Complex" or "End Point" by the CPLD.

A PCI Express block can be instantiated in the FPGA to provide a single PCIe Gen2 port operating as "Root Complex" or "End Point". Only one lane is routed to the PCIe/104 OneBank connector.

"End Point" would be used to communicate with a standard Host, and "Root Complex" would be used to communicate with a peripheral that only implements an "End Point". The Root Complex is usually provided by a host PC, and therefore a typical configuration will have both DSPs and the FPGA configured as End Points.

The global I<sup>2</sup>C bus is connected to the PCIe/104 connector signals SMB\_DAT and SMB\_CLK through a SMBUS to I2C BUS Router within the FPGA. This allows the DSPs to read the carrier board status, and to allow a service processor on the carrier board to read the temperature of the SMT-DSP-GSI board. The Router is required to implement the SMBUS "Address Resolution Protocol" (ARP). This allows I2C device with the same I2C address located on different boards on the PCIe/104 connector stack to communicate with the host board without address conflicts.

The PCIe/104 connector signal SMB\_ALERT is fed to both the FPGA and the CPLD. It is used by the CPLD to assert a DSPA interrupt using a DSPA GPIO signal.

The PCIe/104 connector signal PWRGOOD is fed to both the FPGA and the CPLD. The CPLD uses it to control the power up and down sequencing. In the event of

system power failure, the mains power supply negates PWRGOOD and the CPLD powers down the DSPs with the correct sequence before total power failure.

The PCIe/104 connector signal PE\_RST\_N is fed to the CPLD only. This is the host system reset, and the CPLD uses it to reset the DSPs and other devices without power sequencing.

The PCIe/104 connector signal PSON\_N is fed to both the FPGA and the CPLD. This signal is used by the system host to turn on the primary power supply. Use by SMT-6657 is reserved.

There is no PCIe/104 UP connector because the one bank connector does not provide enough power to supply a second DSP board. This also means there are no automatic link shifting switches required.

#### 3.4 FPGA Interfaces

The FPGA is Xilinx Kintex7 UltraScale FPGA part number: XCKU035-1FBVA676C. The package is designated FBVA676 which is a 27 by 27 ball grid array with 1mm pitch. This device has 312 I/O pins and 16 MGT / GTH gigabit serial ports.

This FPGA primarily provides serial data formatting and LVDS I/O through the FMC daughterboard connector, for interfacing to the data acquisition board.

The FPGA has sufficient processing power to perform complex pre- and postprocessing of sample streams, allowing the processing of raw data to be offloaded from the DSPs:

- 1) > 55000 Xilinx 7 logic slices (equivalent to at least 200000 Xilinx 2 slices)

- 2) 1700 DSP slices

- 3) > 2MB Block RAM

The FPGA implements communication functions appropriate to the installed I/O expansion board. The default use is:

- 4 (four) Optical inputs

- 4 (four) Optical outputs

- 4 (four) TTL inputs

- 4 (four) TTL outputs

- 2 (two) TI DSP Links

- 2 (two) Health LEDs

The board firmware includes two TI comport bridging modules that provide a way for user firmware to send and receive data using TMS320C40 comport signalling conventions. This provides backwards compatibility for users with legacy systems.

The EMIF16 bus timing determines the maximum I/O throughput for each DSP to the FPGA. A DSP running at 1.25GHz clocks the EMIF16 at 208.3MHz, and consecutive reads or writes can be completed in 4 clocks, or 52.085MHz. This makes the EMIF16 peak transfer speed to or from the FPGA, 104.1M Bytes/sec.

For applications that require higher bandwidth between FPGA and DSP, the DSP Universal Parallel Port (UPP) peripheral can be enabled instead of EMIF16. Although UPP has a higher bandwidth (up to 240MB/s) it is DMA driven and has a minimum transfer size of 64 bytes, resulting in a higher latency than EMIF16. UPP is therefore better suited to data-streaming applications than ones which require low latency.

The FPGA has 6 I/O banks each with 52 I/O pins making a total of 312. Each bank can have up to 24 differential pairs. There is also a dedicated configuration bank (0), which can not be used for normal I/O. Each I/O bank can be connected for either 3V3 or 1V8 I/O. It is not possible to mix I/O levels on the same bank. LVDS outputs can only be allocated to banks with 1V8 supply. LVDS inputs can be allocated to 3V3 or 1V8 banks.

The following table lists all FPGA I/O pins including clocks but excluding MGTs. Each pin type is associated with either 3V3 or 1V8 I/O levels. This allocation ensures that all the 3V3 I/O fit exactly with a single bank dedicated to 3V3 I/O and the 5 other banks are all 1V8 I/O. Note that ALL DSP signals are 1V8 only.

The following table gives an example bank allocation of the I/O data and clock (non MGT) pins of the FPGA:

| Inter<br>face        | Signal                             | Standard     | FP<br>GA<br>I/O | B44<br>52x<br>1V8<br>24<br>pairs | B45<br>52x<br>1V8<br>24<br>pairs | B46<br>52x<br>3V3<br>24<br>pairs | B64<br>52x<br>1V8<br>24<br>pairs | B65<br>52x<br>1V8<br>24<br>pairs | B66<br>52x<br>1V8<br>24<br>pairs | Comment                                         |

|----------------------|------------------------------------|--------------|-----------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------------------------------|

| DSPA<br>_EMIF<br>16  | D0-15                              | LVCMOS<br>18 | I/O             |                                  |                                  |                                  |                                  | 16                               |                                  | Must be B65<br>for select MAP<br>config         |

| DSPA<br>_EMIF<br>16  | A0-23                              | LVCMOS<br>18 | IN              |                                  |                                  |                                  |                                  | 24                               |                                  |                                                 |

| DSPA<br>_EMIF<br>16  | CE0-3                              | LVCMOS<br>18 | IN              |                                  |                                  |                                  |                                  | 4                                |                                  |                                                 |

| DSPA<br>_EMIF<br>16  | Controls:<br>R/W, OE,<br>WE, BE0-1 | LVCMOS<br>18 | IN              |                                  |                                  |                                  |                                  | 5                                |                                  |                                                 |

| DSPA<br>_EMIF<br>16  | WAIT0-1                            | LVCMOS<br>18 | OU<br>T         |                                  |                                  |                                  |                                  | 2                                |                                  |                                                 |

| DSPA<br>_EMIF<br>16  | SYSCLKO<br>UT                      | LVCMOS<br>18 | IN              |                                  |                                  |                                  |                                  | 1                                |                                  | 1.25GHz/6=<br>208.3MHz                          |

| DSPB<br>_EMIF<br>16  | D0-15                              | LVCMOS<br>18 | I/O             |                                  |                                  |                                  |                                  |                                  | 16                               |                                                 |

| DSPB<br>_EMIF<br>16  | A0-23                              | LVCMOS<br>18 | IN              |                                  |                                  |                                  |                                  |                                  | 24                               |                                                 |

| DSPB<br>_EMIF<br>16  | CE0-3                              | LVCMOS<br>18 | IN              |                                  |                                  |                                  |                                  |                                  | 4                                |                                                 |

| DSPB<br>_EMIF<br>16  | Controls:<br>R/W, OE,<br>WE, BE0-1 | LVCMOS<br>18 | IN              |                                  |                                  |                                  |                                  |                                  | 5                                |                                                 |

| DSPB<br>_EMIF<br>16  | WAIT0-1                            | LVCMOS<br>18 | OU<br>T         |                                  |                                  |                                  |                                  |                                  | 2                                |                                                 |

| DSPB<br>_EMIF<br>16  | SYSCLKO<br>UT                      | LVCMOS<br>18 | IN              |                                  |                                  |                                  |                                  |                                  | 1                                | 1.25GHz/6=<br>208.3MHz                          |

| DSPA<br>_GPIO        | GPIO00-31                          | LVCMOS<br>18 | I/O             |                                  |                                  |                                  | 32                               |                                  |                                  | Includes SPI<br>(except<br>SPICLK) and<br>UARTS |

| DSPA<br>_SPIC<br>_LK | SPICLK                             | LVCMOS<br>18 | IN              |                                  |                                  |                                  | 1                                |                                  |                                  |                                                 |

| DSPB<br>_GPIO        | GPIO00-31                          | LVCMOS<br>18 | I/O             | 5                                | 8                                |                                  | 19                               |                                  |                                  | Includes SPI<br>(except<br>SPICLK) and<br>UARTS |

| DSPB<br>_SPIC |                          |              |         |    | A  |   |  |                                             |     |

|---------------|--------------------------|--------------|---------|----|----|---|--|---------------------------------------------|-----|

| LK            | SPICLK                   | LVCMOS<br>18 | IN      |    | 1  |   |  |                                             |     |

| FMC           | CLK0_M2C                 | LVDS         | IN      |    | 2  |   |  | Clock FMC<br>module to<br>carrier           |     |

| FMC           | CLK0_C2M                 | LVDS         | OU<br>T | 2  |    |   |  | Clock FMC<br>carrier to<br>module           |     |

| FMC           | LA00_CC                  | LVDS         | IN      |    | 2  |   |  | Clock Source<br>Sync module<br>to carrier   | •   |

| FMC           | LA01_CC                  | LVDS         | OU<br>T | 2  |    |   |  | Clock Source<br>Sync carrier<br>module      |     |

| FMC           | ADC_M2C                  | LVDS         | IN      |    | 16 |   |  | ADC 8 bit<br>double data<br>rate            |     |

| FMC           | FRAME_M<br>2C            | LVDS         | IN      |    | 2  |   |  | ADC Frame<br>data valid bit                 |     |

| FMC           | DAC_C2M                  | LVDS         | OU<br>T | 32 |    |   |  | DAC 16 bit<br>data                          |     |

| FMC           | FRAME_C<br>2M            | LVDS         | OU<br>T | 2  |    |   |  | DAC Frame<br>data valid bit                 |     |

| FMC           | SPICLK,<br>SPICS_C2<br>M | LVDS         | OU<br>T | 4  |    |   |  |                                             |     |

| FMC           | SPID_C2M                 | LVDS         | OU<br>T | 2  |    |   |  | External<br>discrete LVD<br>to LVCMOS       |     |

| FMC           | SPID_M2C                 | LVDS         | IN      | 2  |    |   |  | External<br>discrete<br>LVCMOS18<br>TO LVDS |     |

| FMC           | Interrupt_M<br>2C        | LVDS         | IN      |    | 2  |   |  |                                             |     |

| FMC           | (reserved)               | LVDS         | I/O     |    | 2  |   |  | 34 signal pai<br>on FMC, 1<br>reserved      | irs |

| FMC           | Clock:<br>M2C, C2M       | LVDS         | IN      | 4  |    |   |  | Data clocks                                 |     |

| FMC           | PG_C2M                   | LVTTL        | OU<br>T |    |    | 1 |  | Power good                                  |     |

| I2C           | SDA                      | LVTTL        | I/O     |    |    | 1 |  |                                             |     |

| I2C           | SCL                      | LVTTL        | IN      |    |    | 1 |  |                                             |     |

| CPLD          | RESET_N                  | LVCMOS<br>18 | IN      |    | 1  |   |  |                                             |     |

| PCIe/1<br>04  | PWRGOO<br>D, ALERT       | LVTTL        | IN      |    |    | 2 |  |                                             |     |

| LED           | LED0                     | LVTTL        | OU<br>T |    |    | 1 |  |                                             |     |

| I/O_LS<br>HM  | OPTICALIN<br>0-3         | LVDS         | IN      |    | 8  |   |  |                                             |     |

| I/O_LS<br>HM  | OPTICALO<br>UT0-3        | LVDS         | OU<br>T |    | 8  |   |  |                                             |     |

| I/O_LS<br>HM  | LEDS                     | LVTTL        | OU<br>T |    |    | 2 |  |                                             |     |

| I/O_LS<br>HM        | LVTTL_OU<br>T0-3 | LVTTL        | OU<br>T |    |    | 4  |    |    |    |            |

|---------------------|------------------|--------------|---------|----|----|----|----|----|----|------------|

| I/O_LS<br>HM        | LVTTL_IN0<br>-3  | LVTTL        | IN      |    |    | 4  |    |    |    |            |

| I/O_LS<br>HM        | DSPLINK0         | LVTTL        | I/O     |    |    | 12 |    |    |    |            |

| I/O_LS<br>HM        | DSPLINK1         | LVTTL        | I/O     |    |    | 12 |    |    |    |            |

| I/O_LS<br>HM        | IOENABLE         | LVTTL        | OU<br>T |    |    | 1  |    |    |    |            |

| STAC<br>KPC         | FGPIO0-7         | LVTTL        | OU<br>T |    |    | 8  |    |    |    |            |

| SYNT<br>HESIS<br>ER | STATUS0-<br>1    | LVCMOS<br>18 | IN      | 1  |    |    |    |    |    | PLL_UNLOCK |

| CLOC<br>K           | CLK200MH<br>Z    | LVDS         | IN      |    |    | 2  |    |    |    |            |

| CLOC<br>K           | CLK25M           | LVTTL        | IN      |    |    | 1  |    |    |    |            |

|                     |                  |              |         |    |    |    |    |    |    |            |

| TOTA<br>LS          |                  |              |         | 52 | 52 | 52 | 52 | 52 | 52 | 312        |

## Notes:

This table is one solution to allocating pins to FPGA banks, and is provided to demonstrate that solutions exist. There are other solutions with equal functionality which may be adopted during detailed design, if required due to other constraints. This table only shows the allocation of general I/O pins, it does not show any dedicated pins such as the FPGA configuration interface and Bank 0. Xilinx do not permit allocation of all I/O pins in a bank to differential pairs. 5 Banks are supplied with 1.8V, and 1 Bank is supplied with 3.3V. The postfix "\_N" denotes an active low signal

The following FPGA interface descriptions describe all the FPGA interfaces:

# 3.4.1 FPGA POWER

The supply voltages and tolerances are specified in ref [15] Table 2: Recommended Operating Conditions. The idle no load currents are given in ref [15] Table 6: Typical quiescent Supply Current. The following table estimates FPGA power consumption under 2 conditions: Typical idle no load and maximum power. The maximum power estimates are made with Xilinx Power Estimator ref [16] set to "quick estimate" and process "maximum".

| Supply Volts Typical Typical Max Max |

|--------------------------------------|

|--------------------------------------|

|           |      | Idle  | Idle  | Amps  | Watts |

|-----------|------|-------|-------|-------|-------|

|           |      | Amps  | Watts |       |       |

| Vccint    | 0.95 | 0.907 | 0.862 | 4.237 | 4.025 |

| Vccint_io | 0.95 | 0.077 | 0.073 | 0.285 | 0.270 |

| Vcco_3v3  | 3.30 | 0.001 | 0.003 | 0.302 | 0.996 |

| Vcco_1V8  | 1.80 | 0.001 | 0.002 | 0.302 | 0.543 |

| Vccaux    | 1.80 | 0.145 | 0.261 | 0.295 | 0.531 |

| Vccaux_io | 1.80 | 0.066 | 0.119 | 0.381 | 0.686 |

| Vccbram   | 0.95 | 0.039 | 0.037 | 0.182 | 0.173 |

| TOTAL     | na   | na    | 1.357 | na    | 7.224 |

Note: The 3V3 I/O is only supported by High Range (HR) type pins. Both HR and High Performance (HP) type pins support 1V8 I/O.

Not all of the Vcco power will be consumed in the FPGA chip.

The maximum 0.95V current draw is 4.704A.

The maximum 1.8V current draw is 0.978A.

Control of power sequencing is required both during power up and power down, as specified in the section "Power-On/Off Power Supply Sequencing" in DS892 ref[15]. This control is provided by the CPLD which also controls the DSP power sequencing.

# **3.4.2 FPGA EMIF16**

Each DSP is connected to the FPGA with the EMIF16 bus. This bus consists of a 16 bit bidirectional data bus, a 24 bit address bus, 11 control signals, and the clock signal SYSCLKOUT. This clock is a DSP "System Clock Output" and is the DSP core clock divided by 6, which is the same clock used to time all I/O on the EMIF16 bus. So with a core clock of 1.25GHz, this clock is 208.3MHz or 1/4.8nS.

Texas Instruments have fully specified the EMIF16 bus for asynchronous timing, however by connecting the DSP SYSCLKOUT to the FPGA, it is possible to implement synchronous data transfers. For initial development the FPGA design will implement a 4 clock random read or write, giving a peak transfer rate of 104.1Mbytes/s. During development a 3 clock random read or write will be implemented, giving a peak transfer rate of 138.8Mbytes/s.

For data transfer from DSP to FPGA it is possible to double the data rate by using the EMIF address bus to transfer data. Address signals A00-A15 can be used as an additional 16 bit write only data bus, effectively doubling the write data rate. To allow operation in this mode, address signals A16-23 are used to decode the internal FPGA address space.

The EMIF16 bus from DSPA is used during FPGA configuration to load the configuration data into the FPGA using the Xilinx "Select MAP" interface (ref[17]

"Select MAP configuration modes") , under software control. The DSP software can reconfigure the FPGA at any time.

The FPGA select MAP interface can be 8, 16 or 32 bit so the DSP EMIF16 data bus is connected for 16 bit FPGA configuration. For configuration the EMIF16 data bus must be connected with bits D0-3 on FPGA Bank 0, and D4-15 on FPGA bank 65. However Bank 0 does not support normal I/O after configuration as it is dedicated for configuration only. It is then necessary to ALSO connect EMIF16 data bus D3-0 to bank 65, so these 4 DSPA EMIF16 data bus pins are each connected to 2 FPGA pins. This also applies to the read/write signal EMIFR/W\_N, the output enable signal EMIFOE\_N and the write enable signal EMIFWE\_N. The dedicated FPGA configuration clock is used to clock data in and out on the rising edge. To correctly generate this clock from the EMIF16 control signals, a dedicated high speed NAND gate in the CPLD is used to combine EMIFOE\_N and EMIFWE\_N, so that either generates a rising edge on CCLK at the start of a data transfer.

Here is a table showing connectivity between DSPA EMIF16 and the FPGA to allow configuration read write and I/O read write:

| DSPA      | FPGA | FPGA        | Notes                                   |

|-----------|------|-------------|-----------------------------------------|

| EMIF16    | Bank | Config      |                                         |

| Signal    |      | Pin<br>Name |                                         |

| D0-3      | 0    | D[03:00]    | Configuration data bus                  |

| 005       | 65   | D[05.00]    | I/O data bus                            |

| D4-15     | 65   | D[15:04]    | Configuration and I/O data bus          |

| A0-23     | 65   |             | I/O address bus                         |

| EMIFR/W_N | 0    | RDWR_B      | Configuration read write                |

|           | 65   |             | I/O read write                          |

| EMIFCE0_N | 65   |             | I/O chip select                         |

| EMIFCE1_N | 65   |             | I/O chip select                         |

| EMIFCE2_N | 65   |             | I/O chip select                         |

| EMIFCE3_N | 65   | CSI_B_N     | Configuration interface chip select     |

| EMIFOE_N  | 0    | CCLK        | Configuration clock: NAND with EMIFWE_N |

|           | 65   |             | I/O read output enable                  |

| EMIFWE_N  | 0    | CCLK        | Configuration clock: NAND with EMIFOE_N |

|           | 65   |             | I/O write enable                        |

| EMIFBEO_N | 65   |             | I/O Byte 0 select                       |

| EMIFBE1_N | 65   |             | I/O Byte 1 select                       |

| EMIFWAIT0 | 65   |             | I/O Interrupt 0, or DMA request         |

| EMIFWAIT1 | 65   |             | I/O Interrupt 1, or DMA request         |

| SYSCLKOUT | 65   |             | I/O Clock (Core clock/6)                |

Note: "\_N" denotes an active low signal

Note: There are 52 signals in EMIF16 + SYSCLKOUT which completely fills bank 65

There are 3 other FPGA signals used during Configuration, all are on FPGA bank 0:

PROGRAM\_B is an FPGA input, which starts a new configuration when driven low. This FPGA input is driven by the CPLD.

INIT\_B is a FPGA bidirectional signal which requires an external resistor pull up. This signal is driven low by the FPGA to indicate it is NOT ready to begin receiving configuration data. It can be driven low externally to force the FPGA to delay configuration. After configuration it can be driven low by the FPGA to signal a CRC error. This FPGA output is connected to the CPLD.

DONE is a FPGA bidirectional signal with an external resistor pull up. This pin is driven low by the FPGA until the configuration is complete. A red LED is attached to this signal which is illuminated when DONE is driven low. This FPGA output is connected to the CPLD.

The EMIF16 bus from DSPB completely fills another FPGA bank, which can be chosen for optimum board layout.

The normal operating FPGA data interface consists of a series of memory mapped registers and memory areas which are always available to the DSP software and the DSP DMA engines. There are 2 DSP control inputs EMIFWAIT0 and EMIFWAIT1, and a rising edge from the FPGA on either of these can cause either a DSP software interrupt, or a DSP DMA transfer.

# 3.4.3 FPGA SRIO

Each DSP has 4 SRIO ports, each operates at 5GBits/s, and a single SRIO port is connected from each DSP to the FPGA. All the PCB design rules relating to SRIO interconnect are followed, and because of the short distance, full speed operation is required.

#### 3.4.4 FPGA UART

Each DSP has a dual UART port with each UART having 2 output signals and 2 input signals, making a total of 8 signals. These signals are all connected directly to the FPGA, for optional routing to external board I/O through the FPGA.

# 3.4.5 FPGA DSP GPIO

Each DSP has 32 GPIO pins, and all have a dual function:

| GPIO  | DUAL FUNCTION              |

|-------|----------------------------|

| 00-15 | BOOT CONFIGURATION         |

| 16    | BOOT CONFIGURATION & TIMER |

| 17-19 | TIMER                      |

| 20-27 | UART                       |

| 28-31 | SPI                        |

All 32 of the GPIO pins from each DSP are connected to the FPGA. The boot configuration pins are also connected to the CPLD and are driven by the CPLD during power up and DSP reset. It is essential that the FPGA does not drive any of these signals during this period, as this could interfere with the DSP booting control. During power up the FPGA will not be configured so it can not drive any of these signals. However care is required if the DSP is reset without a power up. To avoid problems the CPLD can force the FPGA PROGRA\_B signal low when the DSP is reset, so the FPGA is guaranteed to be in configure mode and can not drive the DSP BOOT CONFIGURATION signals.

Note that all GPIO signals can be used as interrupts to the DSP, and a number (TBD) of these signals are used as dedicated interrupts.

The DSPA SPI signals are connected to the dedicated FPGA SPI interface.

| GPIO | DSP<br>Normal<br>Function | CPLD/FPGA | Allocated<br>Normal<br>Function | Normal<br>Description        |

|------|---------------------------|-----------|---------------------------------|------------------------------|

| 00   | IO00                      | CPLD      | INTO_TEMP                       | Temperature alarm interrupt  |

| 01   | IO01                      | CPLD      | INT1_ALERT                      | PCIe/104 Alert interrupt     |

| 02   | IO02                      | CPLD      | INT2_PWRGOOD                    | PCIe/104 Powergood interrupt |

| 03   | IO03                      | CPLD      | INT3_DSP                        | Interrupt from the other DSP |

| 04   | IO04                      | CPLD      | DIPSWDAT                        | Serial dipswitch data        |

| 05   | IO05                      | CPLD      | DIPSWCLK                        | Dipswitch clock              |

| 06   | IO06                      | CPLD      | RESETDSP                        | Reset the other DSP          |

| 07   | IO07                      | CPLD      | DSP_INTERRUPT                   | Interrupt to the other DSP   |

| 08   | IO08                      | CPLD      | DSP_WATCHDOG                    | Watchdog software clock      |

| 09   | IO09                      | FPGA      | INT4                            | Interrupt / DMA 4            |

| 10   | IO10                      | FPGA      | INT5                            | Interrupt / DMA 5            |

The following table details the allocation of all GPIO signals between FPGA and CPLD after DSP reset is complete, for both DSPs:

| 11 | IO11     | FPGA | INT6          | Interrupt / DMA 6       |

|----|----------|------|---------------|-------------------------|

| 12 | IO12     | FPGA | INT7          | Interrupt / DMA 7       |

| 13 | IO13     | FPGA | INT8          | Interrupt / DMA 8       |

| 14 | IO14     | FPGA | INT9          | Interrupt / DMA 9       |

| 15 | IO15     | FPGA | INT10         | Interrupt / DMA 10      |

| 16 | Timi0    | FPGA | Reserved FPGA | Reserved for future use |

| 17 | Timi1    | FPGA | Reserved FPGA | Reserved for future use |

| 18 | Timo0    | FPGA | Reserved FPGA | Reserved for future use |

| 19 | Timo1    | FPGA | Reserved FPGA | Reserved for future use |

| 20 | Uartrxd  | FPGA | Uartrxd       | Uart 0 receive data     |

| 21 | Uarttxd  | FPGA | Uarttxd       | Uart 0 transmit data    |

| 22 | Uartcts  | FPGA | Uartcts       | Uart 0 cts              |

| 23 | Uartrts  | FPGA | Uartrts       | Uart 0 rts              |

| 24 | Uartrxd1 | FPGA | Uartrxd1      | Uart 1 receive data     |

| 25 | Uarttxd1 | FPGA | Uarttxd1      | Uart 1 transmit data    |

| 26 | Uartcts1 | FPGA | Uartcts1      | Uart 1 cts              |

| 27 | Uartrts1 | FPGA | Uartrts1      | Uart 1 rts              |

| 28 | Spiscs0  | FPGA | Spiscs0       | SPI chip select 0       |

| 29 | Spiscs1  | FPGA | Spiscs1       | SPI chip select 1       |

| 30 | Spidin   | FPGA | Spidin        | SPI data in             |

| 31 | Spidout  | FPGA | Spidout       | SPI data out            |

The UART pins of both DSPs are reserved for use during development. The SPI pins of DSPA are used for SPI communication to the DSP FPGA only. The SPI pins of DSPB are used for SPI communication to the DSP FPGA only.

# 3.4.6 FPGA PCIe

A single PCIe channel is connected from the FPGA to the PCIe/104 connector. All PCB design rules are followed and full speed operation is required. The PCIe clock is supplied by the PCIe/104 connector.

#### 3.4.7 FPGA MGT to Carrier Board

Four MGT 500MByte/s lanes are connected from the FPGA directly to the StackPC down connector. This can be used to implement a 4 lane PCIe.

#### 3.4.8 FPGA General I/O to Carrier Board

Eight FPGA 3.3V general I/O pins are connected from the FPGA directly to the StackPC down connector. These can be used for triggers, interrupts clocks etc.

## 3.4.9 FPGA PWRGOOD & ALERT

These 3V3 are signals are status inputs to the FPGA and CPLD from the PCIe/104 connector.

PWRGOOD is driven by the system power supply unit (psu) to indicate that the psu outputs and inputs are within tolerance. Since the psu input is the mains supply, this signal provides early warning of impending mains failure and allows the system to take appropriate action.

ALERT is driven by the system board as a software interrupt, routed through the FPGA.

#### 3.4.10 FPGA I2C

Each DSP has a single I2C interface which is connected to all other I2C devices and the FPGA. This is a multi master bus which provides system management connectivity on-board and to selected off-board interfaces:

- DSP A (as bus master)

- DSP B (as bus master)

- Kintex-7 FPGA (as a peripheral and/or bus master)

- Temperature sensor

- Parameter EEPROM memory

- PCIe/104<sup>™</sup> motherboard connector SMBUS router (within the FPGA)

- FMC analog daughterboard connector

- Clock system generator CDCM6208

- Supply voltage monitor 8 channel ADC

As the I<sup>2</sup>C bus is inherently multi master, this allows either DSP to access any I<sup>2</sup>C peripheral.

The I2C bus has 2 signals, clock and data which can be connected to standard FPGA I/O pins, although there may be an advantage in connecting the clock signal to an FPGA clock input.

#### 3.4.11 FPGA SPI

DSPA SPI bus is connected to the DSP FPGA. FMC SPI bus is connected to the DSP FPGA.

DSPA has 2 dedicated SPI chip selects:

SPISCS0 = FMC FPGA SPI select SPISCS1 = DSP FPGA SPI select

When DSP FPGA detects SPISCS0 active it routes the DSPA SPI communication through to the FMC SPI pins. When SPISCS1 is active the SPI communication is routed to the SPI peripheral in the DSP FPGA.

The SPI bus operates a single serial data bit channel at 55.5MBit/s (6.9Mbytes/s) and provides a medium speed communications channel to the FPGA for control and diagnostics. This provides an alternative to using the EMIF16 bus for less time critical communications.

# 3.4.12 FPGA I/O LVDS

There are 4 LVDS I/O outputs and 4 LVDS I/O inputs connected to the 100 way I/O expansion connector. These provide high speed serial communication with the optical interfaces on the I/O board. These optical interfaces are implemented with Avago AFBR-5972Z "Compact 650nm Transceiver with Compact Versatile-Link connector for Fast Ethernet over POF" operating with a Manchester encoded signal at 80MHz. A dedicated 200MHz clock is supplied to the FPGA to enable encoding and decoding.

# 3.4.13 FPGA I/O LEDS

Two 3V3 level LED outputs are connected to the I/O expansion connector to provide front panel status indicators. The LEDs are buffered on the I/O expansion board, so no significant current is passed on these FPGA signals.

# 3.4.14 FPGA I/O LVTTL

32 LVTTL 3V3 I/O signals provide 2 separate 12 bit DSP links, and 4 general purpose outputs and 4 general purpose inputs, through the 100 way I/O expansion connector.

## 3.4.15 FPGA I/O & FMC JTAG

This JTAG interface is defined by Xilinx for serial connection to the DSP FPGA, the DSP CPLD and the FMC FPGA. These 3 devices are chained together so they can all be controlled by this single JTAG interface, which is routed to the 100 way I/O expansion connector. The standard <u>Xilinx Platform Cable USB-II</u> [9] debugging interface connector is located on the I/O expansion board.

To maintain chain integrity when the FMC card is not fitted, a simple analogue switch is used to bypass the FMC connector.

## **3.4.16 FPGA LOCAL LEDS**

One externally buffered LED, colour green, is mounted on the DSP PCB for use in development. This is controlled by a standard FPGA I/O pin, allowing direct software control.

A third LED (colour red) is mounted on the DSP PCB, and is connected to the FPGA "DONE" output, so that it is illuminated when the FPGA is not configured.

Both LEDs are located near to a PCB edge so they can easily be seen.

#### **3.4.17 FPGA FMC LVDS CLOCKS**

Two LVDS clocks are output from the FMC module. One clocks data in to the DSP FPGA and the other clocks data out of the DSP FPGA. Frequencies can be up to 250MHz. The net names are CLK0\_M2C and CLK0\_C2M.

#### 3.4.18 FPGA FMC DATA I/O LA00-33

The FMC LPC interface has 34 signal pairs labelled LA00 to LA33. These are all connected to the FPGA and allocated for use with SMT-FMC311 as follows:

| FMC LA   | FPGA<br>Bank | DSP<br>FPGA<br>IN/OUT | Signal | Description |

|----------|--------------|-----------------------|--------|-------------|

| CLK0_M2C | 45 (GC)      | IN                    |        |             |

| CLK0_C2M | 44 (GC)      | OUT                   |        |             |

| LA00_CC  | 45 (GC)      | IN                    |        |             |

| LA01_CC | 44 (GC) | OUT |             |                                                  |

|---------|---------|-----|-------------|--------------------------------------------------|

| LA02-17 | 44      | OUT | 16 SDATAOUT | Sample data out to DAC                           |

| LA18    | 44      | OUT | SDOUT_FRAME | Framing and valid data out bit                   |

| LA19    | 44      | IN  | SPIDIN      | SPI data in                                      |

| LA20    | 44      | OUT | SPIDOUT     | SPI data out                                     |

| LA21    | 44      | OUT | SPICLK      | SPI clock                                        |

| LA22    | 44      | OUT | SPICS       | SPI chip select (data framing)                   |

| LA23    | 45      | -   | Reserved    | Reserved                                         |

| LA24-31 | 45      | IN  | 8 SDATAIN   | Sample data in from ADC (8 bit double data rate) |

| LA32    | 45      | IN  | SDIN_FRAME  | Framing and valid data in bit                    |

| LA33    | 45      | IN  | INTERRUPT   | Interrupt                                        |

Notes:

All 34 pairs are connected to LVDS I/O capable pins on the FPGA, so that usage for all pairs can easily be changed in the FPGA firmware. This is also required for compatibility with other 3<sup>rd</sup> party FMC boards.

FPGA Bank allocation keeps all bits of each of the following signal groups on a single bank to optimise FPGA internal layout:

DAC data and frame out

ADC data and frame in

SPI bus and controls

To transport sample data, the data is synchronous and clocked using the two LVDS FMC clocks: CLK0\_M2C and CLK0\_C2M.

The input and out FRAME bits are used both to identify channel 1 data, and flag valid data.

The data is always transferred in pairs, channel 1 and 2. The data is only valid when the FRAME bit is valid for channel 1.

# **3.4.19 FPGA FMC SPI**

When SMT-FMC311 is plugged in to the FMC connector, a SPI bus is available for communication, and to configure the FMC FPGA. The DSP FPGA is the SPI bus master.

The SPI channel has 2 uses:

- 1. General purpose data transport e.g. diagnostic data such as captured raw sample data

- 2. To configure the FMC FPGA using the "slave serial" configuration interface

To transport SPI data, the data is synchronous and clocked using SPICLK. This SPI communications channel allows DSPA to communicate with the FMC independently of the sample data channel, and at much higher speed than is possible using the I2C interface. With DSPA core clock at 1.25GHz, the maximum SPICLK frequency is:

$1/(3 \times SYSCLK7)$  or  $1/(3 \times 4.8ns) = 69.4$ MBits/s.

The SPI channel is connected to both the FMC FPGA slave serial configuration interface, and a set of FPGA I/O pins to implement a SPI data slave. Other pins required for the slave serial configuration interface are connected to an I2C I/O port chip. The following table lists all of these connections:

| Signal  | Source              | FMC FPGA configuration pins  | FMC FPGA data slave pins |  |

|---------|---------------------|------------------------------|--------------------------|--|

| SPIDIN  | FMC SPI BUS input   | DOUT                         | I/O data                 |  |

| SPIDOUT | FMC SPI BUS output  | DIN                          | I/O data                 |  |

| SPICLK  | FMC SPI BUS output  | CCLK                         | I/O Clock input          |  |

| PROGRAM | I2C I/O CHIP output | PROGRAM_B                    | none                     |  |

| DONE    | I2C I/O CHIP input  | DONE with pull up resistor   | none                     |  |

| INIT    | I2C I/O CHIP input  | INIT_B with pull up resistor | none                     |  |

An I2C input pin is connected to the FPGA DONE pin, which allows software to confirm the configuration was successful.

An I2C input pin is connected to the FPGA INIT\_B so that software can confirm the state of the FPGA during configuration, and determine if a CRC error occurred during configuration.

The FMC FPGA is configured using the SPI interface and "slave serial" mode. The FMC FPGA is part number XC7A100T, which requires 30606404 bits to configure without compression. At 69.4MHz this process takes 0.441 seconds. With data compression, this process will be faster.

The FMC FPGA requires a low pulse on pin PROGRAM\_B followed by a continuous stream of configuration bits, with bit 0 clocked on the first rising edge of CCLK after PROGRAM\_B goes high. These requirements are met by driving PROGRAM\_B with an output of an I2C parallel port, which is controlled by software. Software then waits until INIT\_B signals the FPGA has finished clearing its previous configuration (if any), then transmits the serial configuration data as a continuous SPI data stream.

# **3.4.20 FPGA FMC INTERRUPTS**

The FMC signal FMC\_INTERRUPT is assigned as an FMC board output, and a DSP board input. It can be configured in software as a real time interrupt or DMA request.

# 3.4.21 FPGA FMC MGT

Eight MGT 500MByte/s lanes are routed from the DSP FPGA to the FMC connector.

#### 3.5 DSP Interfaces

Digital signal processing power is provided by a pair of Texas Instruments <u>TMS320C6657</u> [5] Floating Point DSPs. These DSPs have been selected for their low-power (relative to performance) and low-latency characteristics.

The high clock frequency of 1.25GHz and broad internal parallelism of the TI Keystone DSP CorePac result in a floating-point processing power of up to 20GFlops per core.

Where the SMT-GSI-DSP is embedded in a control loop, this high processing rate minimises the contribution of the DSP to control loop delay.

Compared to previous generations of TI floating-point DSPs, the TMS320C6657 has plentiful internal memory: 1MB of static memory (or cache) per CorePac, with an additional 1MB of on-chip shared memory. This allows most real-time applications to run from on-chip memory, freeing the system design from the non-deterministic behaviour of cached SDRAM, and also reducing the overall power consumption.

The combination of these factors results in the real-world performance of the C6657 core being at least 4x faster than predecessors such as the TMS320C6713, and potentially up to 8x faster. The C6657 supports the instruction set of earlier Texas Instruments floating-point DSPs; recompiling existing software for the new processor architecture will realise further performance gains.

The dual-core architecture of the TMS320C6657 makes it possible for one core to be dedicated to real-time processing, with housekeeping tasks being offloaded to the second core; or for two different filters to be computed at the same time.

Due to the close coupling between DSPs offered by the TI Hyperlink, this approach can be extended to the pairing of DSP A and B – with housekeeping offloaded to DSP A and both cores of DSP B fully available for hard real-time processing.

However the DSPs are not so closely coupled that there is a risk of housekeeping and non-deterministic processing on DSP A interfering with the real-time processing of DSP B. This is one of the advantages of using two TMS320C6657s DSPs rather than a single four-core TMS320C6674; the other main benefit is lower thermal dissipation.

The TMS320C6657 has another key advantage over previous generations of TI floating-point DSP: the availability of Serial RapidIO communication ports which allow DSP systems to be expanded by the addition of processing modules. In the SMTC6657 design, each TMS320C6657 advanced DSP has:

- 2 DSP core subsystems, each performing up to 40G MACs or 20G FLOPs per second

- 64K Byte L1 cache memory per core

- 1024K Byte L2 cache memory per core, also configurable as core-local RAM

- 1024K Byte internal shared memory

- 32 bit DDR3-1333 memory interface with 1G Byte of memory

- 40G bit Hyperlink interface to the other DSP

- Four lanes of SRIO 2.1, each operating up to 5G bit/sec

- One lane connected to the other DSP

- One lane connected to the FPGA

- Two lanes made available to the carrier card stack-down connector.

- A 5G bit/sec PCIe Gen2 x1 interface on the PCIe/104 connector

- EMIF16 Interface to the Xilinx Kintex-7 FPGA

- 16 way GPIO to the Kintex-7 FPGA

- I<sup>2</sup>C interface to a local Temperature sensor, shared parameter memory, on-board and data acquisition module FPGAs, and carrier card.

- JTAG interface for DSP debugging and tracing

- SPI bus interface to the FPGA

- High speed UART (used for development only, routed to the FPGA for optional forwarding to the front panel TTL I/O connector)

DSP A additionally has its 1 gigabit Ethernet port routed to the expansion I/O connector, and access to a large flash memory on its EMIF16 interface.

#### 3.5.1 DSPA Ethernet

DSPA has a single Serial Gigabit Media Independent Interface (SGMII), which is connected to a dedicated Gigabit Ethernet Transceiver (PHY). The recommended part is Marvell 88E1112, because it is used by TI in their C66 EVMs, so the existing TI software will run without modification. It also supports both copper and fibre optic external interfaces at the same time, and it has a small 9mm square package. Both of these external interfaces are connected to the I/O expansion connector, so that the I/O board may implement either or both.

The SGMII interface operates at 1.25GBits/s and requires full impedance control. The PHY should be placed as close as possible to the DSP to minimise routing length. No vias are used to route the SGMII transmit and receive differential pairs.

The single ended PHY clock has strict jitter requirements and is routed with ground shields on either side to prevent cross talk from other signals. The fibre optic data pairs FIN and FOUT also operate at 1.25GBits/s and require full impedance control, and are routed without vias to the 100 way I/O expansion connector.

#### 3.5.2 DSP JTAG

The DSP JTAG implements the standard <u>TI XDS560</u> [8] debugging interface as well as the full system trace back implemented by Texas Instruments in Code Composer Studio 6.x. The 60 way MIPI connector is located on the DSP board adjacent to the DSPs. The TI TMS320C6657 EVM has the TI-60 pin header fitted, however this requires more board space than the MIPI-60. Additionally the Spectrum Digital XDS560V2 emulation pod is supplied with the MIPI-60 connector as standard, and it requires an additional adapter for it to connect to the TI-60 connector.

The interface from both DSPs to the MIPI-60 connector has a total routing length constraint of 3 inches (76.2mm) maximum. The routing requirements are specified in TI document "spru655i.pdf" ref [18]. This is a very important layout constraint.

## 3.5.3 DSP EMIF16

The EMIF16 interface and SYSCLKOUT signal from each DSP is wired directly to the FPGA. The EMIF16 interface from DSPA is also wired to the 256MByte NOR flash. See above section FPGA EMIF16 for more details.

## 3.5.4 DSP UART

Each DSP has a dual UART port with each UART having 2 output signals and 2 input signals, making a total of 8 signals. These signals are all connected directly to the FPGA, for optional routing to external board I/O through the FPGA.

# 3.5.5 DSP GPIO

Each DSP has 32 GPIO pins, which are all connected to the FPGA, with some connected to the CPLD. During DSP reset they are used to set the DSP boot mode by the CPLD. After reset some have dedicated use and some are general purpose I/O. See sections FPGA GPIO and CPLD for more details of these connections.

The DSP GPIO pins are allocated as follows:

| DSP<br>BALL | Reset<br>Bootmode<br>Function | Reset<br>Bootmode<br>Description | GPIO | Normal<br>Function | Normal<br>Description    |

|-------------|-------------------------------|----------------------------------|------|--------------------|--------------------------|

| T25         | Lendian                       | Endian config                    | 00   | IO00               | See CPLD & FPGA sections |

| R25         | Bootmode0                     | Boot device 0                    | 01   | IO01               | See CPLD & FPGA sections |

| R23         | Bootmode1                     | Boot device 1                    | 02   | IO02               | See CPLD & FPGA sections |

| U25         | Bootmode2                     | Boot device 2                    | 03   | IO03               | See CPLD & FPGA sections |

| T23         | Bootmode3                     | Sub mode 0                       | 04   | IO04               | See CPLD & FPGA sections |

| U24         | Bootmode4                     | Sub mode 1                       | 05   | IO05               | See CPLD & FPGA sections |

| T22         | Bootmode5                     | Sub mode 2                       | 06   | IO06               | See CPLD & FPGA sections |

| R21         | Bootmode6                     | Sub mode 3                       | 07   | IO07               | See CPLD & FPGA sections |

| U22         | Bootmode7                     | Sub mode 4                       | 08   | IO08               | See CPLD & FPGA sections |

| U23         | Bootmode8                     | Sub mode 5                       | 09   | IO09               | See CPLD & FPGA sections |

| V23         | Bootmode9                     | Sub mode 6                       | 10   | IO10               | See CPLD & FPGA sections |

| U21         | Bootmode10                    | Sub mode 7                       | 11   | IO11               | See CPLD & FPGA sections |

| T21         | Bootmode11                    | Sub mode 8                       | 12   | IO12               | See CPLD & FPGA sections |

| V22         | Bootmode12                    | Sub mode 9                       | 13   | IO13               | See CPLD & FPGA sections |

| W21         | Pciessmode0                   | PCIe mode 0                      | 14   | IO14               | See CPLD & FPGA sections |

| V21         | Pciessmode1                   | PCIe mode 1                      | 15   | IO15               | See CPLD & FPGA sections |

| AD20        | Pciessen                      | PCIe enable                      | 16   | Timi0              | Timer in 0               |

| AE21        | not used                      | not used                         | 17   | Timi1              | Timer in 1               |

| AC19        | not used                      | not used                         | 18   | Timo0              | Timer out 0              |

| AE20        | not used                      | not used                         | 19   | Timo1              | Timer out 1              |

| AB15        | not used                      | not used                         | 20   | Uartrxd            | Uart 0 receive data      |

| AA15        | not used                      | not used                         | 21   | Uarttxd            | Uart 0 transmit data     |

| AC17        | not used                      | not used                         | 22   | Uartcts            | Uart 0 cts               |

| AB17        | not used                      | not used                         | 23   | Uartrts            | Uart 0 rts               |

| AC14        | not used                      | not used                         | 24   | Uartrxd1           | Uart 1 receive data      |

| AC15        | not used                      | not used                         | 25   | Uarttxd1           | Uart 1 transmit data     |

| AE16        | not used                      | not used                         | 26   | Uartcts1           | Uart 1 cts               |

| AD15 | not used | not used | 27 | Uartrts1 | Uart 1 rts        |

|------|----------|----------|----|----------|-------------------|

| AA12 | not used | not used | 28 | Spiscs0  | SPI chip select 0 |

| AA14 | not used | not used | 29 | Spiscs1  | SPI chip select 1 |

| AB14 | not used | not used | 30 | Spidin   | SPI data in       |

| AB13 | not used | not used | 31 | Spidout  | SPI data out      |