| Unit / Module Description: | Zynq UltraScale MPSoC + 9-axis IMU + 4x FPC |

|----------------------------|---------------------------------------------|

| Unit / Module Number:      | VCS3                                        |

| Document Issue Number:     | 1.1                                         |

| Issue Date:                | 15/07/2025                                  |

| Original Author:           | Paul Dorrell                                |

# VCS3 Application Starter's Guide

Sundance Multiprocessor Technology Ltd, Chiltern House, Waterside, Chesham, Bucks. HP5 1PS.

This document is the property of Sundance and may not be copied or communicated to a third party without prior written permission.

© Sundance Multiprocessor Technology Limited 2025

Application Note: VCS3 Issue 1.1 - Page 1

# **Revision History**

| Issue | Changes Made                                                                                                                       | Date       | Initials |

|-------|------------------------------------------------------------------------------------------------------------------------------------|------------|----------|

| 1.0   | First issue.                                                                                                                       | 18/03/2025 | PD       |

| 1.1   | Added appendix (linked on p6, p39), added note on p38, corrected Fig. 48 to dual parallel flash type, added Fig. 50 and 51 on p42. | 15/07/2025 | NS       |

|       |                                                                                                                                    |            |          |

|       |                                                                                                                                    |            |          |

# **Table of Contents**

| 1 | I   | ntroduction                                                                  | 6  |

|---|-----|------------------------------------------------------------------------------|----|

| 2 | Ι   | Developing for VCS3 using Vivado and Vitis                                   | 6  |

| 3 | F   | Hardware                                                                     | 10 |

|   | 3.1 | How can I setup the Zynq PS interfaces?                                      | 10 |

|   | 3.2 | How can I interface to the IMU?                                              | 12 |

|   | 3.3 | How can I interface with external cameras or displays?                       | 13 |

|   | 3.  | .3.1 j1: camera_a interface                                                  | 13 |

|   | 3.  | .3.2 j3: camera_b interface                                                  | 14 |

|   | 3.  | .3.3 j4: camera_c interface                                                  | 15 |

|   | 3.  | .3.4 j5: camera_d interface                                                  | 16 |

|   | 3.  | .3.5 Using board file for mipi camera serial interface on j1, j3, j4, and j5 | 17 |

|   | 3.  | .3.6 Using board file for mipi display serial interface on j1 and j3         | 18 |

|   | 3.4 | How can I repurpose the board connectors for GPIO?                           | 19 |

|   | 3.5 | What other interfaces are provided?                                          | 20 |

|   | 3.  | .5.1 I2C for monitoring voltage supplies (U7, U13) etc                       | 20 |

|   | 3.  | .5.2 I2C to SPI camera/display control (U6)                                  | 20 |

|   | 3.  | .5.3 J7: can bus                                                             | 21 |

|   | 3.  | .5.4 J9: uart0                                                               | 21 |

|   | 3.  | .5.5 J7: uart1                                                               | 21 |

|   | 3.  | .5.6 J8: uart2                                                               | 22 |

|   | 3.  | .5.7 j8: gpio                                                                | 24 |

|   | 3.6 | How can I create a simple reference hardware design?                         | 25 |

|   | 3.7 | How can I archive and reproduce my simple reference design?                  | 32 |

| 4 | 5   | Software                                                                     | 33 |

|   | 4.1 | Creating Vitis platform component from Vivado hardware                       | 33 |

|   | 4.2 | How can I create a "hello world" app?                                        | 36 |

|   | 4.3 | Running "hello world" app on hardware?                                       | 37 |

|   | 4.4 | How can I create a boot image for "hello world"?                             | 39 |

|   | 4.5 | Selecting boot memory                                                        | 42 |

| 5 | A   | Appendix                                                                     | 42 |

|   | 5.1 | Cloning the GitHub repository                                                | 42 |

|   | 5.2 | Application debug help                                                       | 42 |

# **Table of Figures**

| Figure 1 – Setting path to board files                                | 7  |

|-----------------------------------------------------------------------|----|

| Figure 2 - Creating a new project                                     | 7  |

| Figure 3 – Selecting board file                                       | 8  |

| Figure 4 - Project information in Vivado                              | 8  |

| Figure 5 - Board interfaces in IP Integrator                          | 9  |

| Figure 6 - Running Block Automation in IP Integrator                  | 10 |

| Figure 7 - Zynq configuration after Block Automation                  | 11 |

| Figure 8 – board file mipi camera interfaces                          | 17 |

| Figure 9 – board file mipi display interfaces                         | 18 |

| Figure 10 - board file repurposed gpio interfaces                     | 19 |

| Figure 11 - board file aux uart2 interface                            | 22 |

| Figure 12 - Connection Automation for aux uart2 interface             | 23 |

| Figure 13 - board file aux gpio interface                             | 24 |

| Figure 14 - Selecting VCS3 board file                                 | 25 |

| Figure 15 - VCS3 board interfaces in IP Integrator                    | 26 |

| Figure 16 - Selecting axi_gpio for J1 board interface                 | 27 |

| Figure 17 - Complete reused of all VCS3 board interfaces              | 28 |

| Figure 18 - Running Block Automation for Zynq                         | 29 |

| Figure 19 - Running Connection Automation                             | 29 |

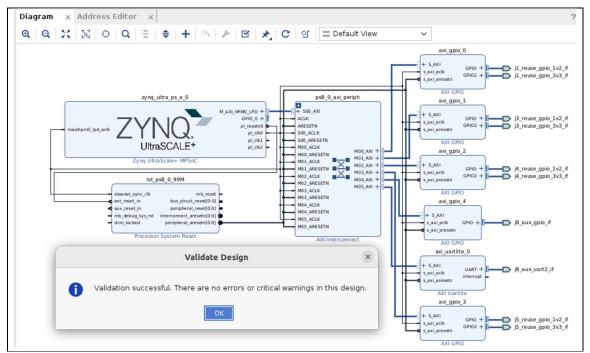

| Figure 20 - Validating block design                                   | 30 |

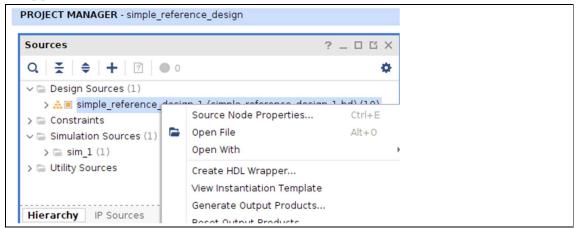

| Figure 21 - Creating block design top level HDL wrapper               | 30 |

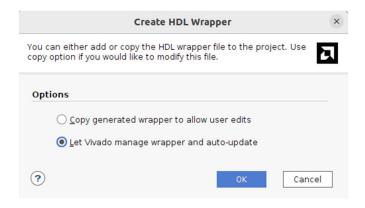

| Figure 22 - Letting Vivado manage top level HDL wrapper               | 31 |

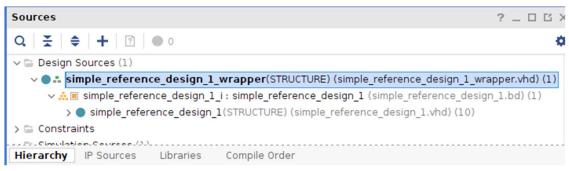

| Figure 23 - Top level wrapper appearing in sources hierarchy          | 31 |

| Figure 24 - Bitstream complete                                        | 31 |

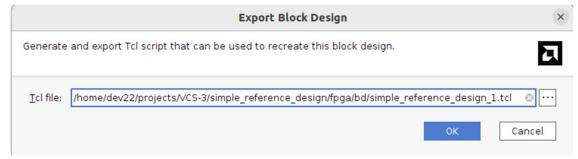

| Figure 25 - Exporting block design as a tcl script                    | 32 |

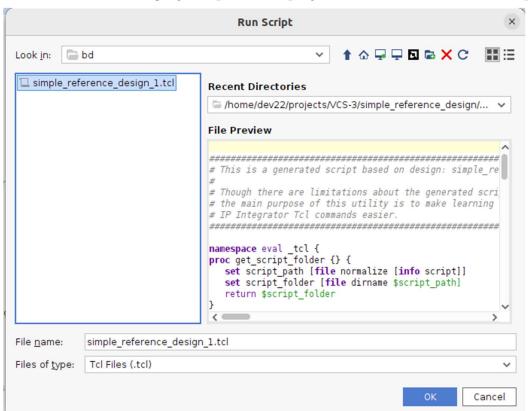

| Figure 26 - Recreating block design using tcl script                  | 32 |

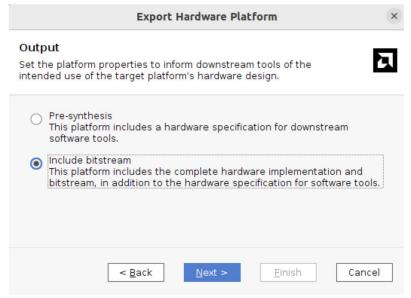

| Figure 27 - Exporting hardware including the bitstream                | 33 |

| Figure 28 - Exporting hardware to a directory where Vitis will use it | 33 |

| Figure 29 - Creating platform in Vitis - naming platform component    | 34 |

| Figure 30 - Creating platform in Vitis - finding .xsa file            | 34 |

| Figure 31 - Creating platform in Vitis - selecting processor and operating system | .35       |

|-----------------------------------------------------------------------------------|-----------|

| Figure 32 - Creating platform in Vitis - summary                                  | .35       |

| Figure 33 - Building platform in Vitis                                            | .35       |

| Figure 34 - Selecting example application                                         | .36       |

| Figure 35 – Creating an application in Vitis – choosing application component na  | me<br>.36 |

| Figure 36 - Creating an application in Vitis - associating hardware platform      | .36       |

| Figure 37 - Creating an application in Vitis - choosing processor domain          | .37       |

| Figure 38 - Creating an application in Vitis - summary                            | .37       |

| Figure 39 - Building application in Vitis                                         | .37       |

| Figure 40 - Running Lynsyn Xilinx Virtual Cable                                   | .38       |

| Figure 41 - VM taking control of required host USB device                         | .38       |

| Figure 42 - Connecting Vitis to Lynsyn Xilinx Virtual Cable                       | .38       |

| Figure 43 - Vitis debug session for helloworld                                    | .39       |

| Figure 44 - Terminal emulator showing output of helloworld                        | .39       |

| Figure 45 - Running Create Boot Image in Vitis                                    | .39       |

| Figure 46 - Create Boot Image in Vitis                                            | .40       |

| Figure 47 - Output of Create Boot Image                                           | .40       |

| Figure 48 – Programming flash in Vitis                                            | .41       |

| Figure 49 - Setting boot mode                                                     | .42       |

| Figure 50 - Creating an SSH key                                                   | .42       |

| Figure 51 - Application debug help                                                | .42       |

## 1 Introduction

This document is a guide for those who own a VCS-3 and would like to develop applications to run on the Zynq MPSoC, either or both the PS (processor side) and the PL (programmable logic). Presented here are basic steps to create simple projects with the various AMD/Xilinx tools.

The hardware development kit is comprehensively described in companion document "VCS3 Development Kit Getting Started Guide". The user is strongly advised to read this as it contains details of JTAG debug setup needed for application development.

# 2 Developing for VCS3 using Vivado and Vitis

The VCS3 has been used in two versions of Vivado, 2022.2 and 2023.2. Although the Zynq MPSoC XCZU3EG device has been supported since 2017.x, it is recommended always to use a newer version.

Sundance Multiprocessor Technology LTD provides documentation and resources in GitHub:

https://github.com/SundanceMultiprocessorTechnology/

Board files from Sundance are accessible at repository:

https://github.com/SundanceMultiprocessorTechnology/VCS-3/tree/main/board\_files

To include the board files in your system, download the corresponding files. They can be added at the installation path of Vivado, normally:

<installationpath>/Xilinx/Vivado/2023.2/data/xhub/boards

Old version of the tool used the following path:

<installationpath>/Xilinx/Vivado/20XX.X/data/boards/board\_files/

Depending on how these files are copied, you may need to change the access privilege to allow Vivado to access them, for example:

```

root@Ubuntu-22-04:/tools/Xilinx/Vivado/2023.2/data/xhub/boards/Sundance#

chmod -R a+rX *

```

Furthermore, the above command may not work unless you have already elevated yourself to root using the command:

```

dev22@Ubuntu-22-04:/$ su

Password:

root@Ubuntu-22-04:/# whoami

root

```

NOTE: all the examples shown in this guide use Vivado 2023.2 and Vitis

[If you encounter issues when cloning the repository, see section 5.1]

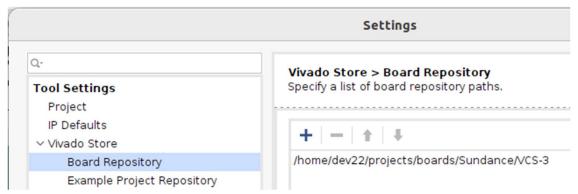

An easier way to install the board files in your system is to tell Vivado where you have copied them using the Tools Settings as shown in this example.

*Figure 1 – Setting path to board files*

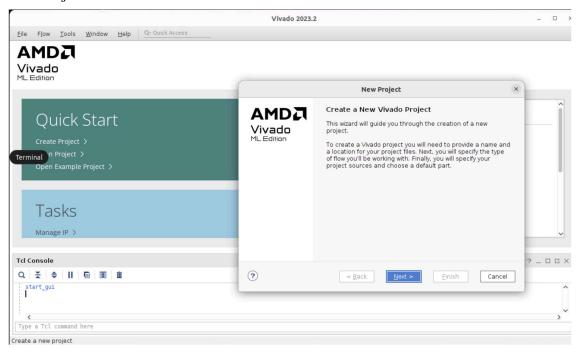

Having Vivado open, create a new project, either on "Create Project", or File→Project→New:

Figure 2 - Creating a new project

Click "Next" and select the path of the project.

Choose RTL project and mark the square "Do not specify sources at this time" in case the user doesn't require importing any source and it's a blank project.

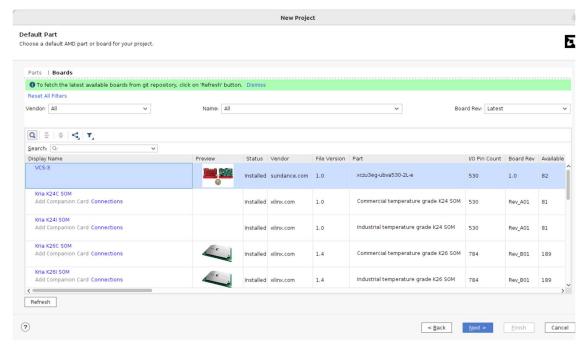

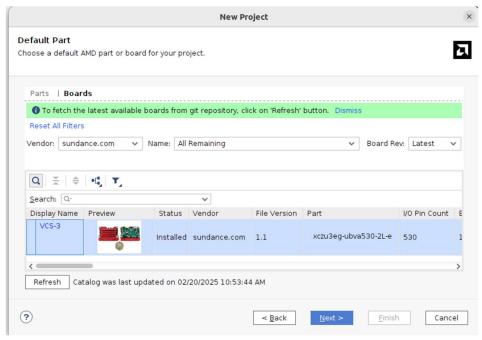

Then, when Vivado asks for a device part, select "Boards", and choose the corresponding board files.

Figure 3 – Selecting board file

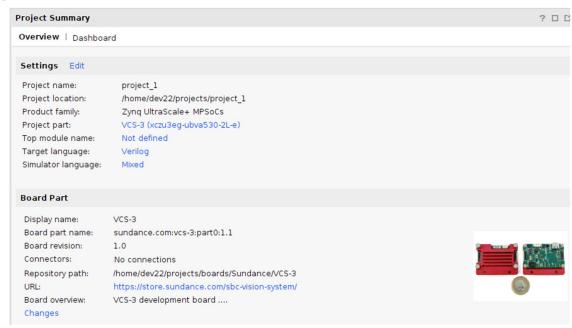

Once the project is opened, the user can see the information about the board and the part used:

Figure 4 - Project information in Vivado

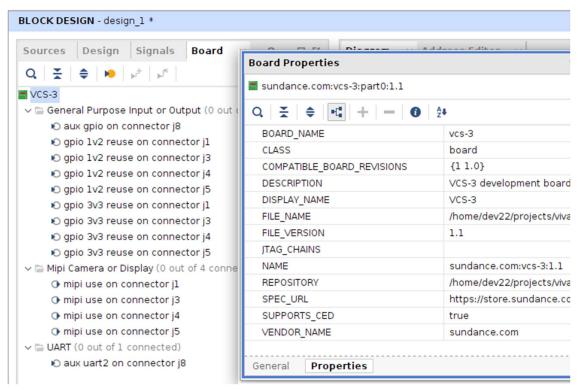

As soon as the user creates a new block design in IP Integrator, there will be some interfaces available, already set up and ready to use:

Figure 5 - Board interfaces in IP Integrator

The board interfaces available are those connected to the PL side of the Zynq. Other board interfaces are accessible through the Zynq PS MIO pins as described in the Hardware section.

## 3 Hardware

In addition to "VCS3 Development Kit Getting Started Guide" the following sections show the raw pinout from the FPGA to peripherals or board connectors. However, board files are provided to make it easier for the application developer to interface to certain off-board peripheral such as cameras or displays. The board files also offer an easy way to repurpose board connector as general purpose io.

#### 3.1 How can I setup the Zynq PS interfaces?

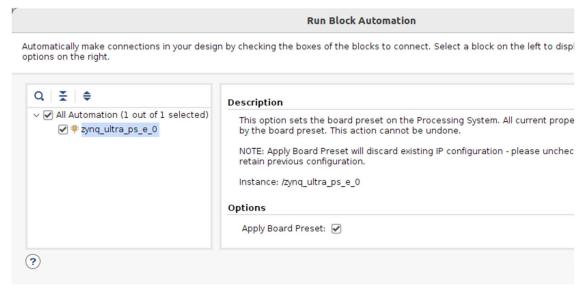

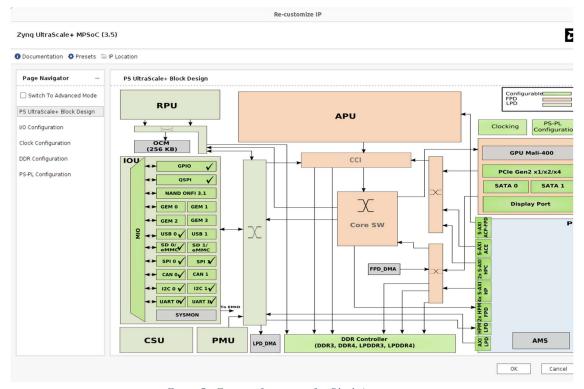

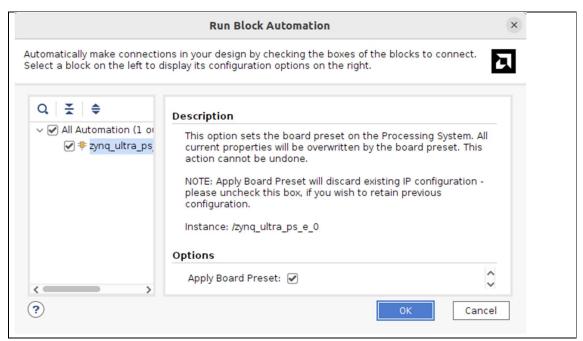

The processor side interfaces are easily setup by ensuring that "Apply Board Preset" is selected when adding "Zynq UltraScale+ MPSoc" IP core to your design and running "Block Automation":

Figure 6 – Running Block Automation in IP Integrator

The resulting configuration can be viewed by recustomizing this block and cancelling when finished.

#### The preset configures PS interfaces for

- Clocks into programmable logic (PL) @ 100MHz, 200MHz, and 25MHz

- Quad SPI Flash

- SD (eMMC)

- CAN

- I2C

- SPI x2

- UART x2

- GPIO (x21 to PS pins, x1 into PL)

- Timer/counter x3

- USB (including USB 3.0)

- LPDDR4 memory controller

Figure~7-Zynq~configuration~after~Block~Automation

#### 3.2 How can I interface to the IMU?

The onboard 9-axis Inertial Measurement Unit (DS-000189-ICM-20948-v1.3.pdf) is connected using the following FPGA pins:

| IMU device pin name | IMU device pin | board net name | connection type   | FPGA pin | note         |

|---------------------|----------------|----------------|-------------------|----------|--------------|

| /CS                 | U5:22          | IMU_SS0        | direct connection | A12      | PS_MIO67_502 |

| SCL/SCLK            | U5:23          | IMU_SCLK       | direct connection | B15      | PS_MIO64_502 |

| SDA/SDI             | U5:24          | IMU_MOSI       | direct connection | A14      | PS_MIO69_502 |

| SDO/AD0             | U5:9           | IMU_MISO       | direct connection | A13      | PS_MIO68_502 |

| FSYNC               | U5:11          | IMU_FSYNC      | direct connection | B19      | PS_MIO70_502 |

| INT1                | U5:12          | IMU_INT        | direct connection | A15      | PS_MIO71_502 |

This peripheral is selected automatically when "Zynq UltraScale+ MPSoC" IP is added to a block design and the board preset is applied. It can then be accessed by PS software using SPI 0.

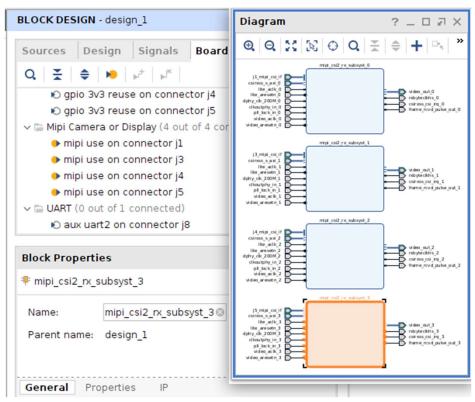

#### 3.3 How can I interface with external cameras or displays?

Four identical connectors (<u>J1, J3, J4, and J5</u>) can be used for any combination of external cameras and displays. These use the MIPI (Mobile Industry Processor Interface) standard, CSI (camera serial interface) or DSI (display serial interface). The following four connection tables are for CSI with the data lanes as inputs from the camera. For DSI, the connections are similar except that the data lanes are outputs to the display.

For each connector, data lanes are matched in length to within 0.5mm.

SPI control to each connector is done via an I2C to SMBus switch (pca9546a.pdf)

#### 3.3.1 j1: camera\_a interface

| MIPI net name | connector pin | board net name | connection type                    | FPGA pin | note                             |

|---------------|---------------|----------------|------------------------------------|----------|----------------------------------|

| CSI_CLK0_P    | J1:9          | CAM_A_CK_P     | direct connection                  | N6       |                                  |

| CSI_CLK0_N    | J1:8          | CAM_A_CK_N     | direct connection                  | P6       |                                  |

| CSI_DATA0_P   | J1:3          | CAM_A_D0_P     | direct connection                  | N4       |                                  |

| CSI_DATA0_N   | J1:2          | CAM_A_D0_N     | direct connection                  | P4       |                                  |

| CSI_DATA1_P   | J1:6          | CAM_A_D1_P     | direct connection                  | M7       |                                  |

| CSI_DATA1_N   | J1:5          | CAM_A_D1_N     | direct connection                  | N7       |                                  |

| CSI_DATA2_P   | J1:12         | CAM_A_D2_P     | direct connection                  | Т6       |                                  |

| CSI_DATA2_N   | J1:11         | CAM_A_D2_N     | direct connection                  | U5       |                                  |

| CSI_DATA3_P   | J1:15         | CAM_A_D3_P     | direct connection                  | T4       |                                  |

| CSI_DATA3_N   | J1:14         | CAM_A_D3_N     | direct connection                  | U4       |                                  |

|               | J1:17         | CAM_A_EN       | direct connection                  | K15      | Under control of PS side of Zynq |

|               | J1:18         | CAM_A_CLK_28   | via resistive divider              | D10      | CAM_A_CLK                        |

|               | J1:20         | CAM_A_SCL      | indirect connection via I2C mux U6 | J11      | CAM_SCL                          |

|               | J1:21         | CAM_A_SDA      | indirect connection via I2C mux U6 | M10      | CAM_SCD                          |

# 3.3.2 j3: camera\_b interface

| MIPI net name | connector pin | board net name | connection type                    | FPGA pin | note                             |

|---------------|---------------|----------------|------------------------------------|----------|----------------------------------|

| CSI_CLK0_P    | J3:9          | CAM_B_CK_P     | direct connection                  | T2       |                                  |

| CSI_CLK0_N    | J3:8          | CAM_B_CK_N     | direct connection                  | U2       |                                  |

| CSI_DATA0_P   | J3:3          | CAM_B_DO_P     | direct connection                  | N2       |                                  |

| CSI_DATA0_N   | J3:2          | CAM_B_DO_N     | direct connection                  | N1       |                                  |

| CSI_DATA1_P   | J3:6          | CAM_B_D1_P     | direct connection                  | R1       |                                  |

| CSI_DATA1_N   | J3:5          | CAM_B_D1_N     | direct connection                  | T1       |                                  |

| CSI_DATA2_P   | J3:12         | CAM_B_D2_P     | direct connection                  | V4       |                                  |

| CSI_DATA2_N   | J3:11         | CAM_B_D2_N     | direct connection                  | V3       |                                  |

| CSI_DATA3_P   | J3:15         | CAM_B_D3_P     | direct connection                  | K7       |                                  |

| CSI_DATA3_N   | J3:14         | CAM_B_D3_N     | direct connection                  | K6       |                                  |

|               | J3:17         | CAM_B_EN       | direct connection                  | M12      | Under control of PS side of Zynq |

|               | J3:18         | CAM_B_CLK_28   | via resistive divider              | D9       | CAM_B_CLK                        |

|               | J3:20         | CAM_B_SCL      | indirect connection via I2C mux U6 | J11      | CAM_SCL                          |

|               | J3:21         | CAM_B_SDA      | indirect connection via I2C mux U6 | M10      | CAM_SCD                          |

# 3.3.3 j4: camera\_c interface

| MIPI net name | connector pin | board net name | connection type                    | FPGA pin | note                             |

|---------------|---------------|----------------|------------------------------------|----------|----------------------------------|

| CSI_CLK0_P    | J4:9          | CAM_C_CK_P     | direct connection                  | K2       |                                  |

| CSI_CLK0_N    | J4:8          | CAM_C_CK_N     | direct connection                  | L1       |                                  |

| CSI_DATA0_P   | J4:3          | CAM_C_D0_P     | direct connection                  | L2       |                                  |

| CSI_DATA0_N   | J4:2          | CAM_C_D0_N     | direct connection                  | M1       |                                  |

| CSI_DATA1_P   | J4:6          | CAM_C_D1_P     | direct connection                  | G7       |                                  |

| CSI_DATA1_N   | J4:5          | CAM_C_D1_N     | direct connection                  | H7       |                                  |

| CSI_DATA2_P   | J4:12         | CAM_C_D2_P     | direct connection                  | J1       |                                  |

| CSI_DATA2_N   | J4:11         | CAM_C_D2_N     | direct connection                  | K1       |                                  |

| CSI_DATA3_P   | J4:15         | CAM_C_D3_P     | direct connection                  | Н8       |                                  |

| CSI_DATA3_N   | J4:14         | CAM_C_D3_N     | direct connection                  | J7       |                                  |

|               | J4:17         | CAM_C_EN       | direct connection                  | N9       | Under control of PS side of Zynq |

|               | J4:18         | CAM_C_CLK_28   | via resistive divider              | D13      | CAM_C_CLK                        |

|               | J4:20         | CAM_C_SCL      | indirect connection via I2C mux U6 | J11      | CAM_SCL                          |

|               | J4:21         | CAM_C_SDA      | indirect connection via I2C mux U6 | M10      | CAM_SCD                          |

# 3.3.4 j5: camera\_d interface

| MIPI net name | connector pin | board net name | connection type                    | FPGA pin | note                             |

|---------------|---------------|----------------|------------------------------------|----------|----------------------------------|

| CSI_CLK0_P    | J5:9          | CAM_D_CK_P     | direct connection                  | H2       |                                  |

| CSI_CLK0_N    | J5:8          | CAM_D_CK_N     | direct connection                  | H1       |                                  |

| CSI_DATA0_P   | J5:3          | CAM_D_D0_P     | direct connection                  | G2       |                                  |

| CSI_DATA0_N   | J5:2          | CAM_D_D0_N     | direct connection                  | G1       |                                  |

| CSI_DATA1_P   | J5:6          | CAM_D_D1_P     | direct connection                  | F7       |                                  |

| CSI_DATA1_N   | J5:5          | CAM_D_D1_N     | direct connection                  | G6       |                                  |

| CSI_DATA2_P   | J5:12         | CAM_D_D2_P     | direct connection                  | E1       |                                  |

| CSI_DATA2_N   | J5:11         | CAM_D_D2_N     | direct connection                  | F1       |                                  |

| CSI_DATA3_P   | J5:15         | CAM_D_D3_P     | direct connection                  | C1       |                                  |

| CSI_DATA3_N   | J5:14         | CAM_D_D3_N     | direct connection                  | D1       |                                  |

|               | J5:17         | CAM_D_EN       | direct connection                  | K12      | Under control of PS side of Zynq |

|               | J5:18         | CAM_D_CLK_28   | via resistive divider              | C13      | CAM_D_CLK                        |

|               | J5:20         | CAM_D_SCL      | indirect connection via I2C mux U6 | J11      | CAM_SCL                          |

|               | J5:21         | CAM_D_SDA      | indirect connection via I2C mux U6 | M10      | CAM_SCD                          |

#### 3.3.5 Using board file for mipi camera serial interface on j1, j3, j4, and j5

*Figure 8 – board file mipi camera interfaces*

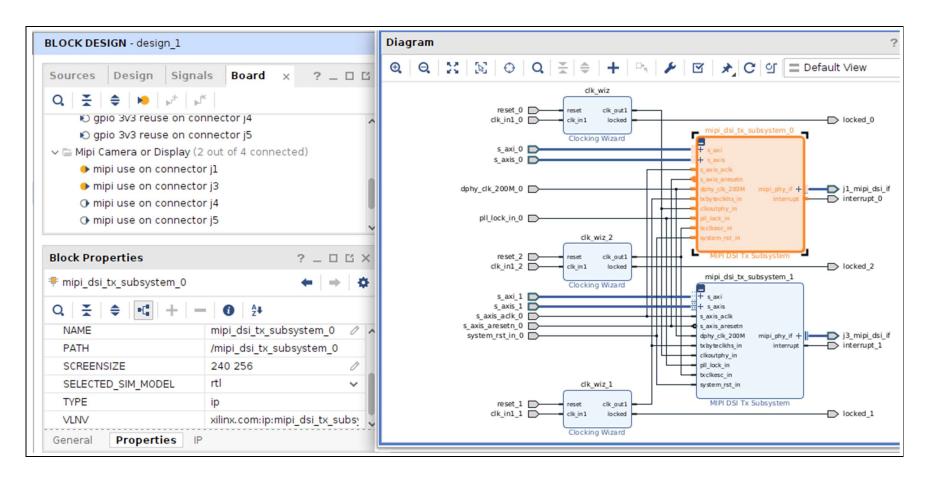

#### 3.3.6 Using board file for mipi display serial interface on j1 and j3

*Figure 9 – board file mipi display interfaces*

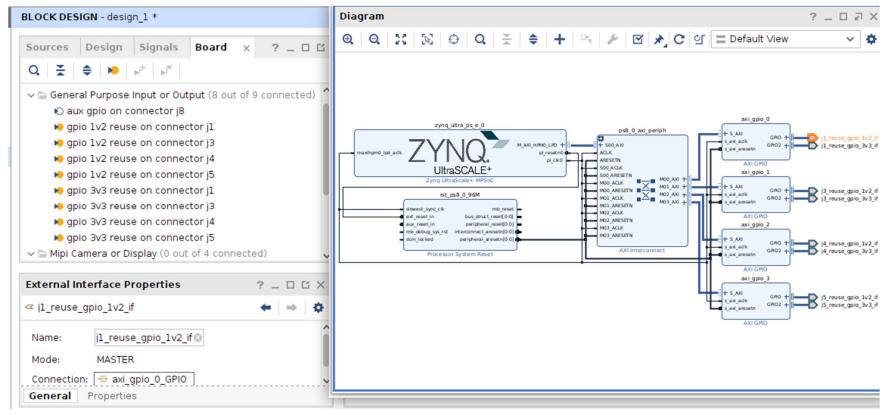

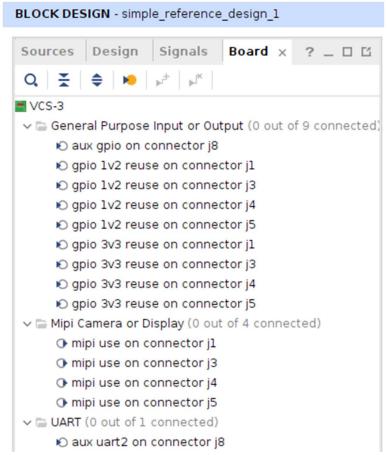

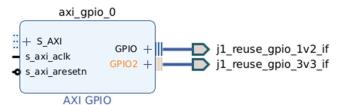

#### 3.4 How can I repurpose the board connectors for GPIO?

Any of the four identical connectors (J1, J3, J4, and J5) can be repurposed for "General Purpose IO" using the Board tab. The image below shows a complete repurpose of all four. Note that one pin in each connector is at 3v3 logical standard and handled by the GPIO2 interface of each respective "AXI GPIO".

*Figure 10 – board file repurposed gpio interfaces*

#### 3.5 What other interfaces are provided?

#### 3.5.1 I2C for monitoring voltage supplies (U7, U13) etc

| Device pin | board net name | connection type   | FPGA pin | PS pin                          |

|------------|----------------|-------------------|----------|---------------------------------|

| U7:4       | SCL            | direct connection | A18      | PS_MIO74_502                    |

| U13:4      |                |                   |          | Pulled up to 1V8 using 10k ohms |

| U27:8      |                |                   |          |                                 |

| U21: G7    |                |                   |          |                                 |

| U11:9      |                |                   |          |                                 |

| U7:1       | SDA            | direct connection | A16      | PS_MIO75_502                    |

| U13:1      |                |                   |          | Pulled up to 1V8 using 10k ohms |

| U27:7      |                |                   |          |                                 |

| U21: H8    |                |                   |          |                                 |

| U11:8      |                |                   |          |                                 |

This peripheral is selected automatically when "Zynq UltraScale+ MPSoC" IP is added to a block design and the board preset is applied. It may be accessed from PS software as I2C 0.

## 3.5.2 I2C to SPI camera/display control (U6)

| Device pin | board net name | connection type   | FPGA pin | PS pin                          |

|------------|----------------|-------------------|----------|---------------------------------|

| U6:14      | CAM_SCL        | direct connection | J11      | PS_MIO28_501                    |

|            |                |                   |          | Pulled up to 3V3 using 4k7 ohms |

| U6:15      | CAM_SDA        | direct connection | M10      | PS_MIO29_501                    |

|            |                |                   |          | Pulled up to 3V3 using 4k7 ohms |

This peripheral is selected automatically when "Zynq UltraScale+ MPSoC" IP is added to a block design and the board preset is applied. It may be accessed from PS software as I2C 1.

#### 3.5.3 J7: can bus

#### <u>J7</u>

| connector pin connection type |                     | board net name | FPGA pin            | PS pin       |

|-------------------------------|---------------------|----------------|---------------------|--------------|

| J7:4                          | indirect connection | CAN_RXD        | K10                 | PS_MIO51_501 |

| J7:5                          | indirect connection | CAN_TXD        | XD J10 PS_MIO50_501 |              |

|                               |                     | CAN_SCLK       | M13                 | PS_MIO44_501 |

|                               |                     | CAN_MOSI       | M14                 | PS_MIO49_501 |

|                               |                     | CAN_MISO       | N12                 | PS_MIO48_501 |

|                               |                     | CAN_SS0        | N13                 | PS_MIO47_501 |

This peripheral is selected automatically when "Zynq UltraScale+ MPSoC" IP is added to a block design and the board preset is applied. It may be accessed from PS software as SPI 1.

#### 3.5.4 **J9**: uart0

#### <u>J9</u>

| connector pin | board net name | connection type   | FPGA pin | PS pin       |

|---------------|----------------|-------------------|----------|--------------|

| Ј9:2          | UARTO_RX       | direct connection | K14      | PS_MIO30_501 |

| Ј9:3          | UARTO_TX       | direct connection | J12      | PS_MIO31_501 |

This peripheral is selected automatically when "Zynq UltraScale+ MPSoC" IP is added to a block design and the board preset is applied. It may be accessed from PS software as UART 0.

#### 3.5.5 J7: uart1

#### <u>J7</u>

|   | connector pin | board net name | connection type   | FPGA pin | PS pin       |

|---|---------------|----------------|-------------------|----------|--------------|

|   | J7:1          | UART1_RX       | direct connection | M9       | PS_MIO32_501 |

| Ī | J7:2          | UART1_TX       | direct connection | H14      | PS_MIO33_501 |

This peripheral is selected automatically when "Zynq UltraScale+ MPSoC" IP is added to a block design and the board preset is applied. It may be accessed from PS software as UART 1.

**Application Note: VCS3**

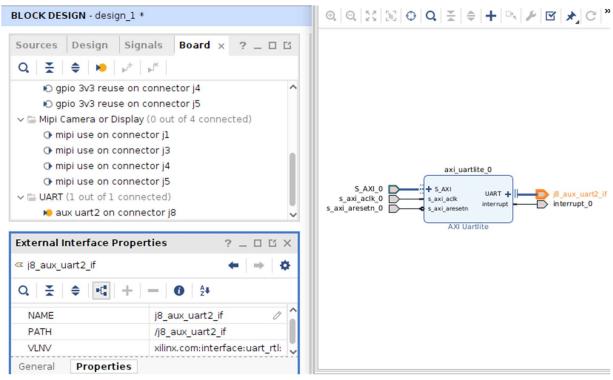

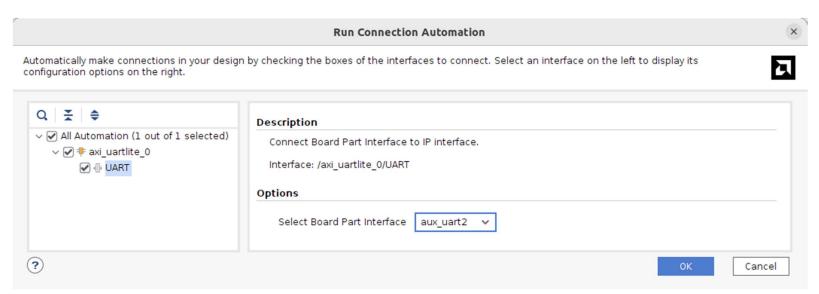

#### 3.5.6 J8: uart2

#### <u>J8</u>

| connector pin | board net name | connection type   | FPGA pin | note |

|---------------|----------------|-------------------|----------|------|

| J8:2          | AUX_UART2_RX   | direct connection | B10      |      |

| J8:3          | AUX_UART2_TX   | direct connection | C10      |      |

This peripheral is selected when the "aux uart2 on connector j8" is selected from the Board tab or when "AXI Uartlite" IP is added to a block design.

Figure 11 – board file aux uart2 interface

Figure 12 – Connection Automation for aux uart2 interface

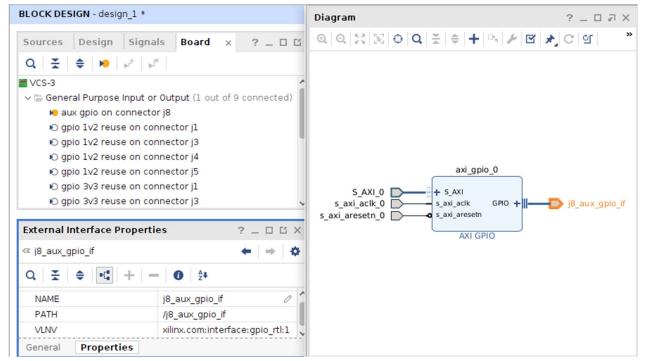

#### 3.5.7 j8: gpio

| connector pin | board net name | connection type   | FPGA pin | note |

|---------------|----------------|-------------------|----------|------|

| J8:4          | GPIO0          | direct connection | В9       |      |

| J8:5          | GPIO1          | direct connection | A11      |      |

| J8:6          | GPIO2          | direct connection | A10      |      |

| J8:7          | GPIO3          | direct connection | A9       |      |

This peripheral is selected when either the "aux gpio on connector j8" is selected from the Board tab or when "AXI GPIO" IP is added to a block design:

*Figure 13 – board file aux gpio interface*

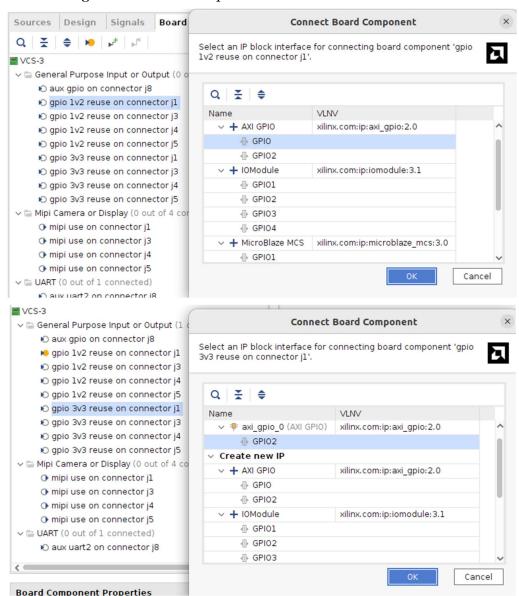

#### 3.6 How can I create a simple reference hardware design?

A simple reference design is created here using the board files described above. Open Vivado to create a new project and, when invited to choose a part or board, select the VCS-3.

Figure 14 – Selecting VCS3 board file

Once the project is created click "Create Block Design" and give it a meaningful name.

Notice the Board tab in Block Design window is populated with a range of possible board interfaces.

Figure 15 – VCS3 board interfaces in IP Integrator

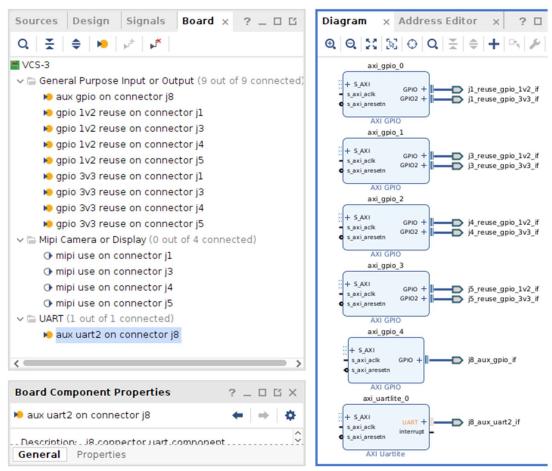

For this simple design we'll use all the board connectors for gpio and uarts.

Here j1 is selected and connected to an axi\_gpio IP core, the 1v2 logic to the first IP port and 3v3 logic to the second IP port.

Figure 16 – Selecting axi gpio for J1 board interface

Doing the same for all the other connectors ...

Figure 17 – Complete reused of all VCS3 board interfaces

After adding a Zynq UltraScale+ MPSoC core to the block design you are invited to use "Designer Assistance": Run Block Automation and Run Connection Automation.

Block Automation configures the Zynq with board presets and ensures connectivity from the PS side pins to respective peripherals.

Figure 18 – Running Block Automation for Zynq

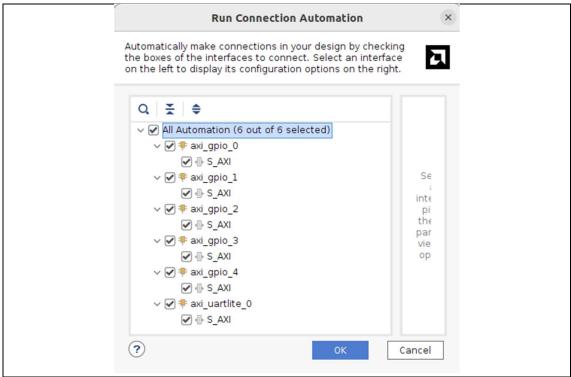

Connection Automation wires up all the selected IP cores.

Figure 19 – Running Connection Automation

The resulting block design can be validated using menu Tools→Validate Design

Figure 20 – Validating block design

The block design can now be closed and saved. When it appears in the Project Manager Sources window Hierarchy, you can right click it to select "Create HDL Wrapper".

Figure 21 – Creating block design top level HDL wrapper

Choosing to let Vivado manage the wrapper is usually the better option unless you want to add other HDL entities (VHDL) or modules (Verilog) to the top level.

Figure 22 – Letting Vivado manage top level HDL wrapper

Figure 23 – Top level wrapper appearing in sources hierarchy

The generated wrapper here is in VHDL but it could be in Verilog if the project default HDL had been set to that.

To generate the complete hardware project just select "Generate Bitstream" in the Project Manager window and choose Yes or OK to any popup dialog boxes. This process will:

- Generate output products for each IP core in the block diagram

- Run synthesis for each of them and also the top level HDL wrapper

- Run Implementation (place and route)

- Produce a bitstream that can be downloaded to the VCS3

The whole process may take some time ... relax! You'll know when it's finished when you see this in the top right corner of Vivado:

Application Note: VCS3

# 3.7 How can I archive and reproduce my simple reference design?

Vivado makes it easy for you to archive your block design as a tcl scripts (tcl stands for Tool Command Language). You just need to create the script using menu File→Export→Export block Design.

Figure 25 – Exporting block design as a tcl script

To recreate the block design, just open a new project for VCCS-3 and run the script.

Figure 26 – Recreating block design using tcl script

You can then recreate the top level wrapper and generate the bitstream as before. The above tcl script is saved in the VCS-3 archive for you to try.

## 4 Software

Before any software can be written for the VCS3 processor side (PS) the hardware developed previously must be exported from Vivado and imported into Vitis.

#### 4.1 Creating Vitis platform component from Vivado hardware

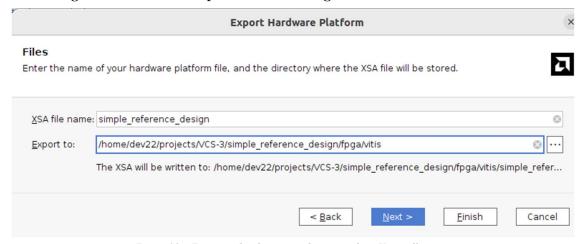

To export the hardware use menu File→Export→Export Hardware

Figure 27 - Exporting hardware including the bitstream

Continuing with the above simple reference design ...

Figure 28 – Exporting hardware to a directory where Vitis will use it

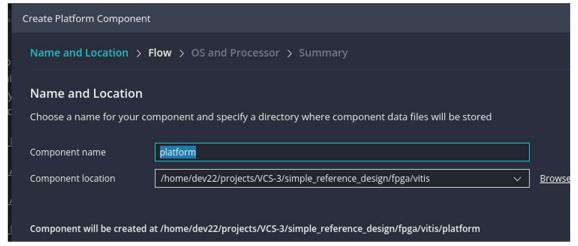

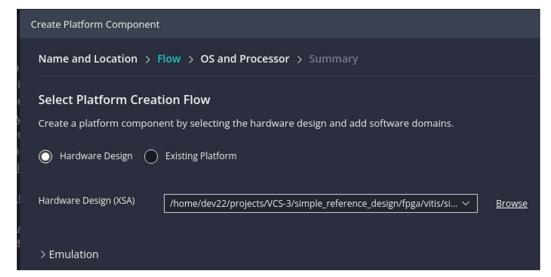

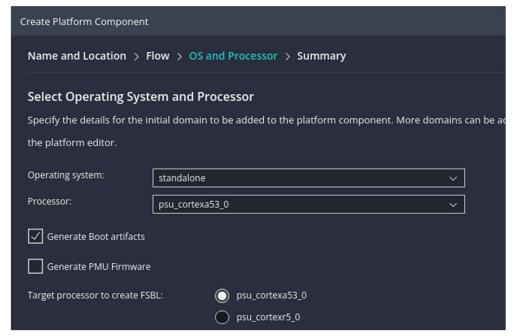

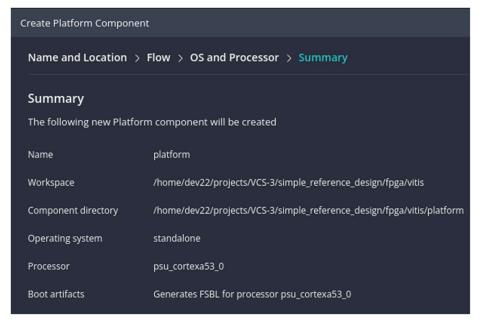

When starting Vitis you must choose a working directory. Then to import the above hardware .xsa file use menu File→New Component→Platform and follow the sequence of dialogs.

Figure 29 – Creating platform in Vitis – naming platform component

Figure 30-Creating platform in Vitis-finding .xsa file

Figure 31 – Creating platform in Vitis – selecting processor and operating system

Figure 32 – Creating platform in Vitis – summary

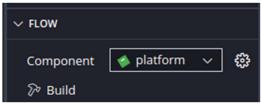

This platform component can now be built by clicking the Build icon

Figure 33 – Building platform in Vitis

#### 4.2 How can I create a "hello world" app?

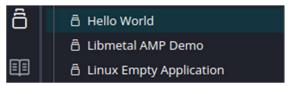

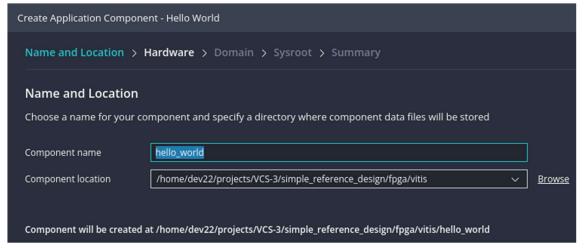

There are a few options to creating a new software application. One of the easiest is to copy an example application and elaborate it to your own specification. To do this click on the examples icon and select one of the many preprepared applications e.g. "Hello World" and following the sequence of dialogs.

Figure 34 – Selecting example application

Figure 35 – Creating an application in Vitis – choosing application component name

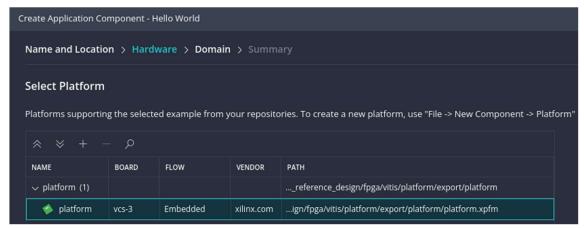

Figure 36 – Creating an application in Vitis – associating hardware platform

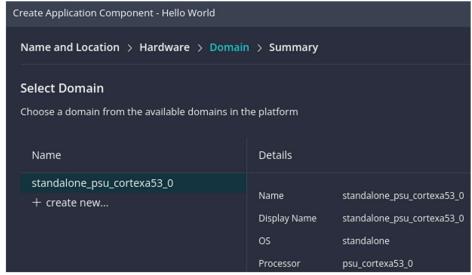

Figure 37 – Creating an application in Vitis – choosing processor domain

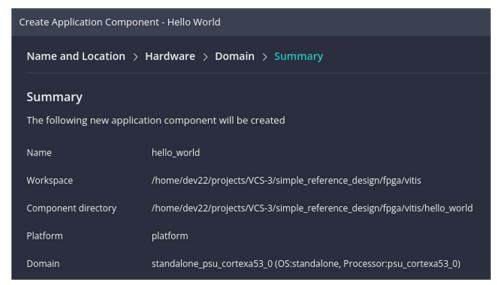

Figure 38 – Creating an application in Vitis – summary

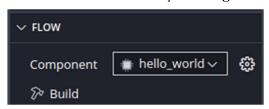

This application component can now be built by clicking the Build icon

Figure 39 – Building application in Vitis

# 4.3 Running "hello world" app on hardware?

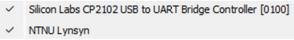

The built application can now be downloaded and run on the VCS3 hardware depending on your JTAG connection. If you have the VCS3 development kit (as described in "VCS3 Development Kit Getting Started Guide") then the easiest way is to invoke the Lynsyn Xilinx Virtual Cable driver as shown here.

NOTE: If you are not using the VCS3 Development Kit (i.e. not using the Lynsyn), skip to debug session.

```

dev22@Ubuntu-22:~/projects Q = - □ ×

dev22@Ubuntu-22:~/projects$ sudo lynsyn_xvc

[sudo] password for dev22:

INFO: To connect to this lynsyn_xvc instance, use url: TCP:Ubuntu-22:2542

```

Figure 40 – Running Lynsyn Xilinx Virtual Cable

If running Vitis from a VM don't forget to claim the required USB devices from the host machine..

Figure 41 – VM taking control of required host USB device

So that Vitis can use the Lynsyn, open a terminal using menu Terminal→New Terminal and invoke xsct and run command line: connect -xvc-url localhost:2542

```

OUTPUT × DEBUG CONSOLE × TASK: XSDB CONSOLE DEV22@UBUNTU-22: ~/PROJECTS/VCS-3/SIMPLE_REFERENCE_DESIGN/FPGA/VITIS > dev22@Ubuntu-22: ~/projects/VCS-3/simple_reference_design/fpga/vitis$ xsct

DEV22@UBUNTU-22: ~/PROJECTS/VCS-3/SIMPLE_REFERENCE_DESIGN/FPGA/VITIS × ojects with new python command line tool.

Use "vitis -s <script>" (script mode) and "xsct% connect -xvc-url localhost:2542

```

Figure 42 – Connecting Vitis to Lynsyn Xilinx Virtual Cable

#### The debug session can now be started ...

```

15:36:04 INFO : XSDB server has started successfully from frontend.

15:36:05 INFO : Connection to XSDB Server established.

15:36:05 INFO : connect -url tcp:127.0.0.1:3121

15:36:05 INFO : Done

15:36:13 INFO : bpremove -all

15:36:13 INFO : Context for 'APU' is selected.

15:36:14 INFO : System reset is completed.

15:36:17 INFO : 'after 3000' command is executed.

15:36:17 INFO : 'targets -set -filter {jtag_cable_name =~ "Xilinx Virtual Cable localhost:2542" && level==0 && jtag_device_ctx=="jsn-XVC-localhost:2542-14710093-0"}' command

is executed.

15:36:53 INFO

: Device configured successfully with "/home/dev22/projects/VCS-

3/simple_reference_design/fpga/vitis/hello_world/_ide/bitstream/simple_reference_design.bit"

INFO

loadhw

/home/dev22/projects/VCS-

-hw

3/simple_reference_design/fpga/vitis/platform/export/platform/hw/simple_reference_design.xsa

{0x40000000 0x5ffffffff} {0x1000000000

-mem-ranges [list {0x80000000 0xbfffffff}}

0x7fffffffff]

15:36:53 INFO : targets -set -nocase -filter {name =~"APU*"}

15:36:53

INFO

/home/dev22/projects/VCS-

source

3/simple\_reference\_design/fpga/vitis/hello\_world/\_ide/psinit/psu\_init.tcl

15:37:06 INFO : psu_init

15:37:07 INFO : after 1000

15:37:08 INFO : psu_ps_pl_isolation_removal 15:37:09 INFO : after 1000

15:37:09 INFO : psu_ps_pl_reset_config

15:37:09 INFO : targets -set -nocase -filter {name =~ "*A53*#0"}

```

```

15:37:11 INFO : rst -processor

15:37:15 INFO : dow /home/dev22/projects/VCS-

3/simple_reference_design/fpga/vitis/hello_world/build/hello_world.elf

15:37:15 INFO : bpadd main

15:37:16 INFO : con

15:37:17 INFO : Testing the connection for 127.0.0.1

```

... and halts at the source code entry point:

Figure 43 – Vitis debug session for helloworld

If a terminal emulator is attached to the Lynsyn USB serial device, the message can be seen from the application when run

Figure 44 – Terminal emulator showing output of helloworld

[If you encounter issues when debugging, see section 5.2]

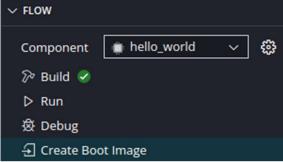

### 4.4 How can I create a boot image for "hello world"?

Simply by selecting "Create Boot Image" in the Flow window ...

Figure 45 – Running Create Boot Image in Vitis

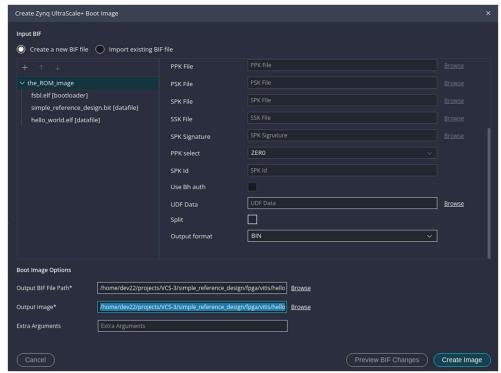

$\dots$  and following dialog. Here we don't bother about encryption so most of the fields are empty.

Figure 46 – Create Boot Image in Vitis

The result of selecting "Create Image" is a .bin file called "BOOT.bin" and a .bif file, in this case, called "hello\_world.bif"

Figure 47 – Output of Create Boot Image

The bif file is simply a recipe for creating the bin file from three images:

- first stage boot loader (FSBL) .elf file

- programmable logic (PL) firmware application .bit file

- processor side (PS) software application .elf file

```

//arch = zynqmp; split = false; format = BIN

the_ROM_image:

{

[bootloader, destination_cpu = a53-0]/home/dev22/projects/VCS-

3/simple_reference_design/fpga/vitis/platform/export/platform/sw/boot/fsbl.elf

[destination_device = pl]/home/dev22/projects/VCS-

3/simple_reference_design/fpga/vitis/hello_world/_ide/bitstream/simple_reference_design.bit

[destination_cpu = a53-0, exception_level = e1-3]/home/dev22/projects/VCS-

3/simple_reference_design/fpga/vitis/hello_world/build/hello_world.elf

}

```

The .bif file can be reused to recreate the .bin file when any image is changed.

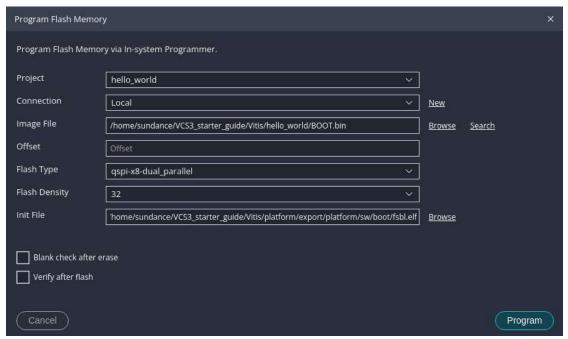

The .bin file can be programmed into eMMC or SPI ROM memory on the VCS3 using menu Vitis→Program Flash.

Figure 48 – Programming flash in Vitis

The process of erasing flash, programming verifying may take some time ... but you can monitor progress in the Output window:

#### 4.5 Selecting boot memory

By setting dual switch SW1 on the VCS3 as described below, the Zynq device will be configured from the selected memory when powering up the board.

| Switch 1 | Switch 2 |          |

|----------|----------|----------|

| OFF      | OFF      | JTAG     |

| ON       | OFF      | eMMC     |

| OFF      | ON       | QSPI ROM |

| ON       | ON       |          |

Figure 49 – Setting boot mode

# 5 Appendix

Additional information to catch and help solve potential issues.

#### 5.1 Cloning the GitHub repository

Cloning the <a href="https://github.com/SundanceMultiprocessorTechnology/VCS-3.git">https://github.com/SundanceMultiprocessorTechnology/VCS-3.git</a> repository may be difficult because of access permissions.

- o In terminal:

- · git init

- · git config --global user.name < GitHub account username >

- · git config --global user.email < GitHub account email>

- ssh-keygen -t ed25519 -C your email@example.com

- eval "\$(ssh-agent -s)"

- ssh-add ~/.ssh/id ed25519

- cat ~/.ssh/id\_ed25519.pub

- o Go to: https://github.com/settings/keys

- Click "New SSH key"

- Paste your key and give it a name (e.g., "My Linux Laptop")

- o Back in the terminal, clone repository using:

- git clone git@github.com:SundanceMultiprocessorTechnology/VCS-3.git

Figure 50 - Creating an SSH key

#### 5.2 Application debug help

- Flow > Debug > Open Settings

- · Check that 'FSBL' is selected next to 'Board Initialisation'

- Click 'Debug' in the Flow window.

- Once the debug program has stopped at the source code entry point, click 'Continue' or press F5 to complete the debug.

- Observe the 'Hello world' message in your PuTTy (or alternate output if not using PuTTy) terminal!

Figure 51 – Application debug help

| If FSBL Board Initialisation mode fails, fully power cycle the board and retry. |  |  |  |  |  |  |

|---------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |

|                                                                                 |  |  |  |  |  |  |