Description

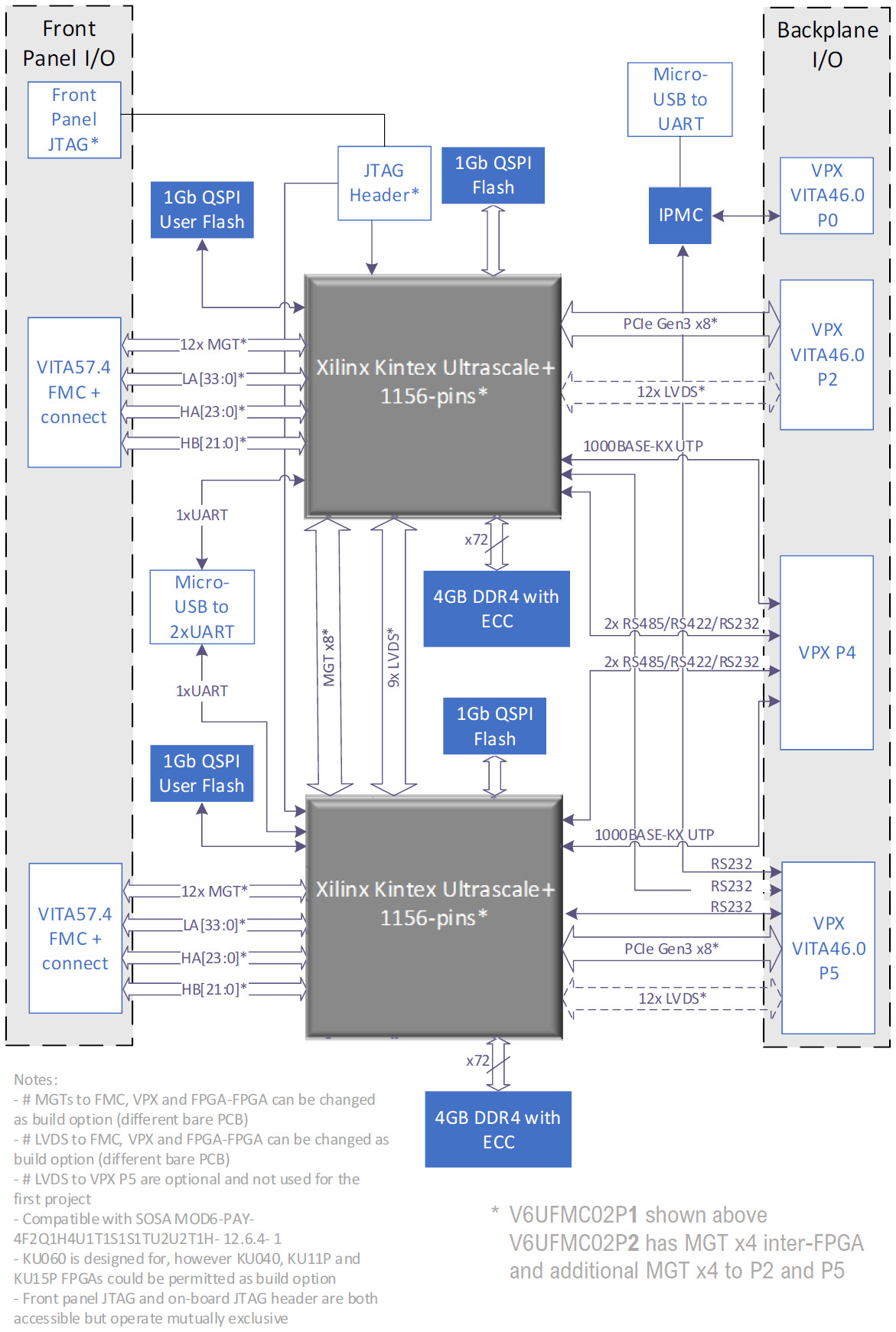

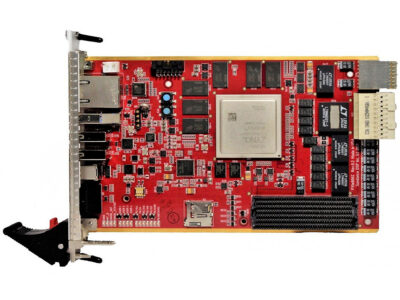

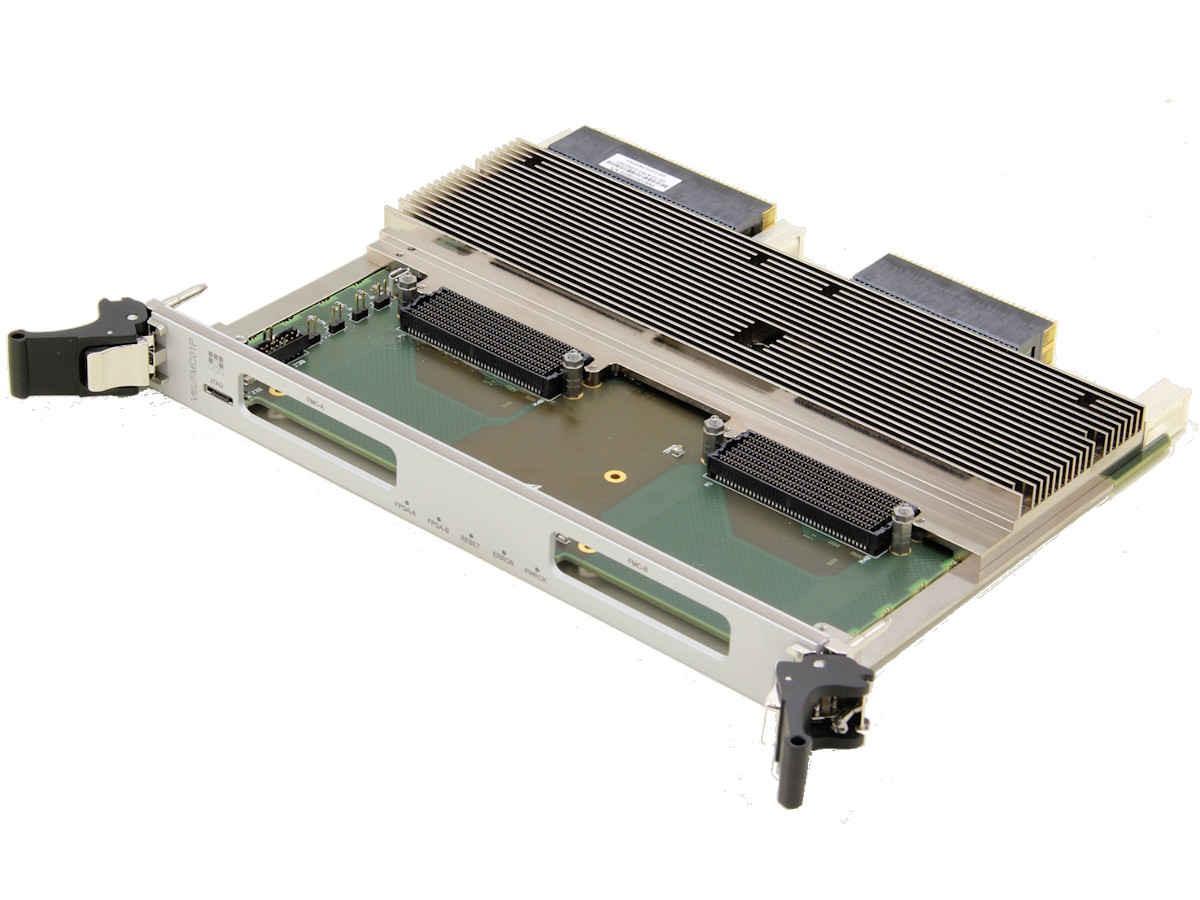

The 6U V6UFMC02P is a member of Hybrid DSP’s XU02P 1156 Core Series of mid-range, cost-effective, rugged processing boards based on the AMD Kintex UltraScale+ A1156 FPGA package, up to 8GB DDR4 per FPGA and an ARMbased Board Management Controller (BMC).

The V6UFMC02P is available with a range of build options for OpenVPX air and conduction-cooled-based systems and those aligned with the SOSA Technical Standard. Features include two FMC+ sites to support mezzanine cards with I/O routing to either the front panel or optionally VITA 66/67 optical/coax blind mate connectors on the backplane.

In addition to numerous standard build options, the design is optimized for rapid customization of many key features, including the front panel, cooling solution, reference firmware, and BMC. Furthermore, the PCB layout and stack-up allow for a viable low-risk route for more complex technical and commercial requirements, including modular to monolithic.

What’s Included?

- Python API and reference application

- VHDL based reference design

- Vivado reference project

Specifications

Main Processor and Memory

- AMD Kintex UltraScale™ A1156 FPGA XCKU11P, XCKU15P (Dual)

- DDR4 4GB or 8GB with ECC (per FPGA)

Board Management

- Voltage and temperature monitor

- Power/reset control

- Tier-2 VITA 46.11 IPMI

Backplane Architecture (6U)

- Up to 12 serial transceiver lanes on VPX P2 and P5 (PCIe Gen3, Aurora, Ethernet, RapidIO etc)

- Up to 12 LVDS on VPX P2 and P5

- VITA 65.0 and SOSA aligned slot profiles

- VITA 66/67 Optical and Coaxial options

Front Panel I/O

- Two FMC+ sites per VITA 57.4

- Extended component-free region

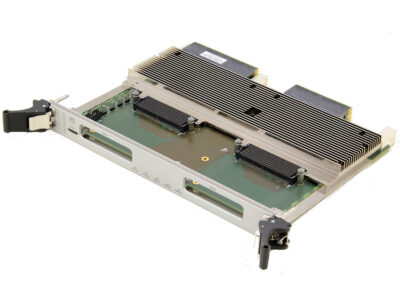

Mechanical

- 6U VPX COTS and Custom air and conduction-cooled (FMC+) compatible heat-frame

- OpenVPX and VPX-REDI

- Pitch: 1” and 0.8”

Board Support Package

- Vivado project, VHDL based reference designs, UART and PCIe drivers, API, Python and C/C++ sample applications

Compliance

- OpenVPX System Specification encompasses VITA 46.0, 46.3, 46.4, 46.6, 46.7, 46.9, 46.11

- Compatible with VITA 65 and SOSA aligned systems

- VITA 47.0

- VITA 48.0/48.1/48.2 (REDI)

- VITA 57.4

VITA 47.0 Construction, Safety and Quality

- Environmental Class: EAC1, EAC6, ECC1 and ECC3 (-40 C to +70 C operating temperature range)

- IPC-A-610D Class 3 and IPC-A-600G Class 3

- Conformal Coating: IPC-CC-830B

AMD UltraScale+ FMC+ Carrier

AMD UltraScale+ FMC+ Carrier