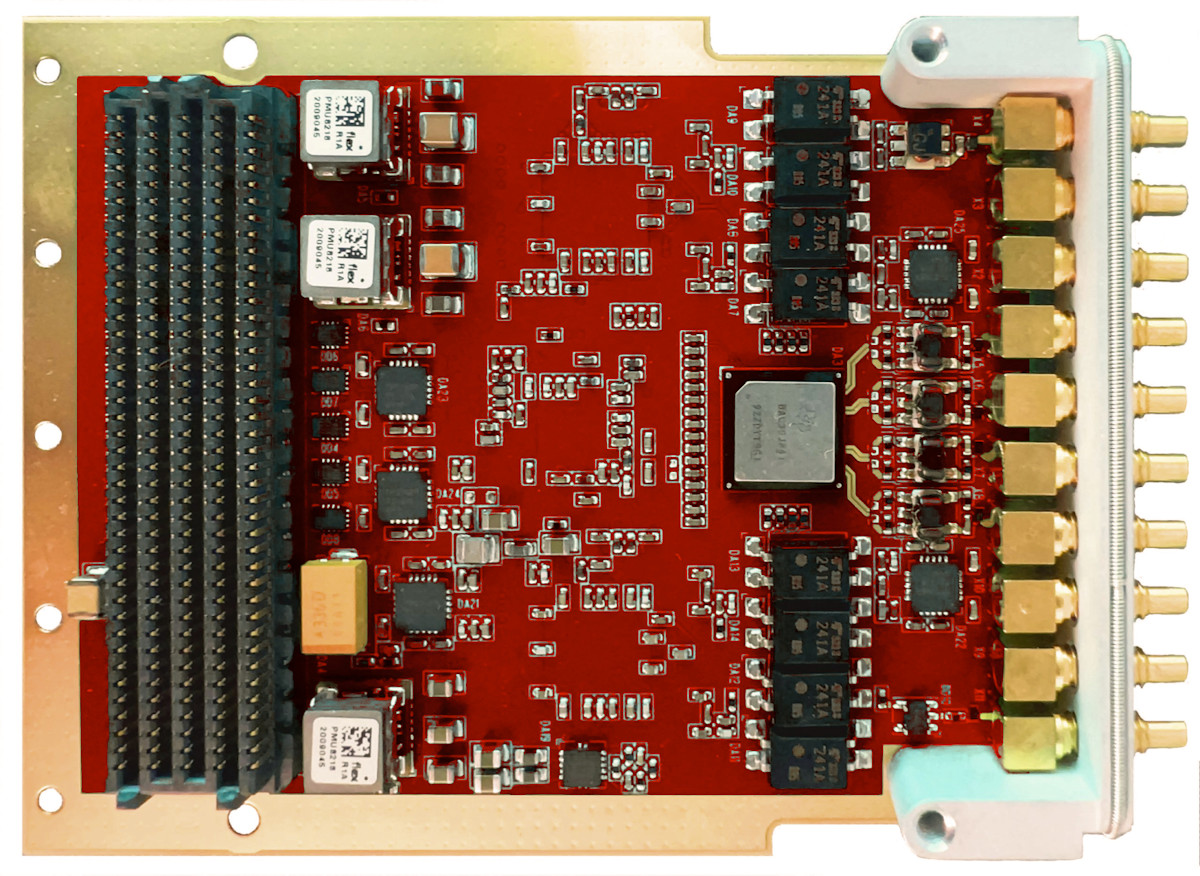

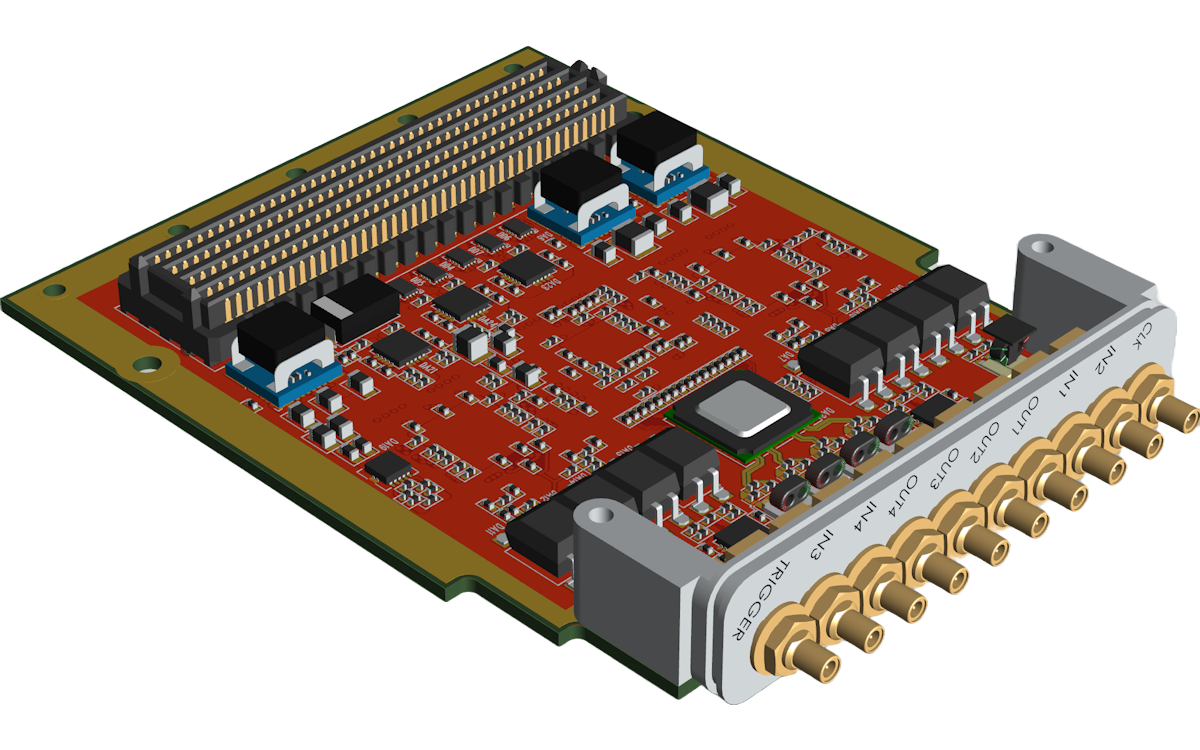

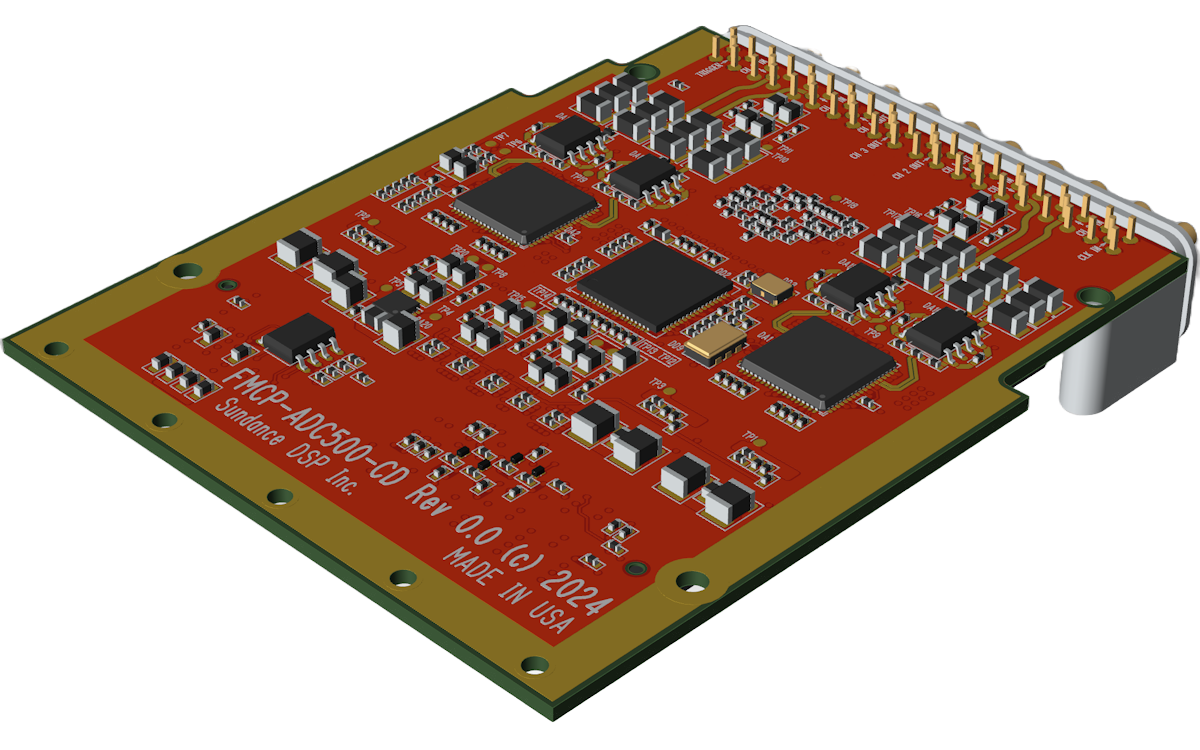

Description

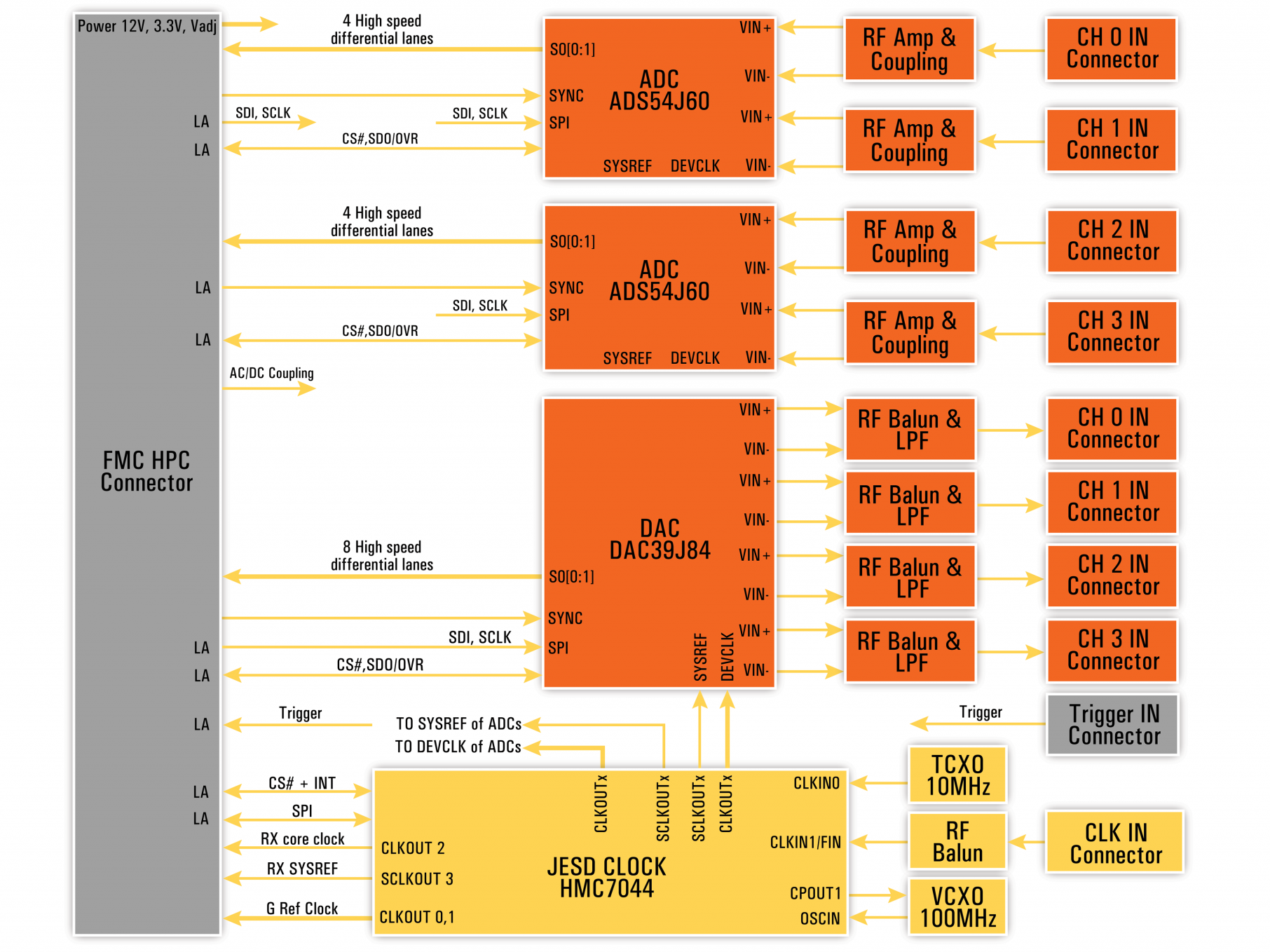

The FMC-ADC500CD is a cutting-edge HPC FMC module that offers 4 channels of high sampling rate and high-resolution ADC and DAC. Both the ADC and DAC interface to a carrier board using a JESD204B interface. The inputs of the ADC and the outputs of the DAC can be changed from AC coupled to DC coupled on the fly.

This board is designed for high-performance data acquisition and signal generation applications that require precise synchronization and low latency. It features the following components:

- HMC7044 from ADI: This is the main clock distribution IC that provides multiple clock outputs with SYSREF signals. It can clock JESD204B devices with subclass 1 synchronization.

- ADS54J60 from TI: These are dual-channel, 16-bit, 1-GSPS ADCs that support JESD204B interface. They can operate at various sample rates and enable decimation for lower bandwidth applications.

- DAC39J84 from TI: This is a quad-channel, 16-bit, 2.8-GSPS DAC that supports JESD204B interface. It can generate direct IF or RF signals with high dynamic range and low distortion.

- External trigger input: This allows adding timestamps to the sample stream from the ADCs for accurate timing measurements.

- Internal VCXO and TCXO clocks: These provide stable and low-jitter reference clocks for the board. The HMC7044 also generates SYSREF signals with known and adjustable delay for JESD204B synchronization.

With this board, you can achieve high-speed data conversion, signal generation, and synchronization for your applications. It is ideal for radar, wireless communication, test and measurement, and other demanding scenarios.