Description

NES-IPCORE-CAN Implements a CAN bus controller that performs serial communication according to CAN 2.0, and specifications. It supports the original Bosch protocol and ISO specifications as defined in ISO 1989 including time triggered operation (TTCAN) as specified in ISO 19898 4 and is also optimized to support the popular AUTOSAR and SAE J1939 specifications. The CAN protocol uses a multi master bus configuration for the transfer of frames between nodes of the network and manages error handling with no burden on the host processor.

The core enables the user to set up economic and reliable links between various components.

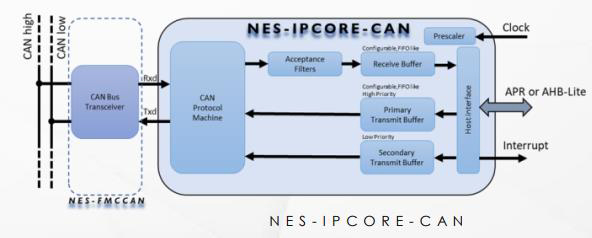

It appears as a memory mapped I/O device to the host processor, which accesses the CAN core to control the transmission or reception of frames. The NES IPCORE CAN core is easy to use and integrate, featuring programmable interrupts, data and baud rates; a configurable number of independently programmable acceptance filters; and a generic processor interface or optionally an AMBA APB, or AHB Lite interface. It implements a flexible buffering scheme, allowing fine-tuning of the core size to satisfy the requirements of each specific application. The number of receive buffers is synthesis time configurable.

Two types of transmit buffers are implemented: a high-priority primary transmits buffer (PTB) and a lower-priority secondary transmit buffer (STB).

The PTB can store one message, while the number of included buffer slots for the STB is synthesis time configurable. The transmit buffer can operate in FIFO or priority mode. An optional wrapper instantiating multiple CAN controller cores eases integration in cases where multiple bus nodes need to be controlled by the same host processor. mode extensions, providing error analysis, diagnosis, system maintenance, and optimization features.

The NES IPCORE CAN core is extensively verified and proven in multiple production designs.