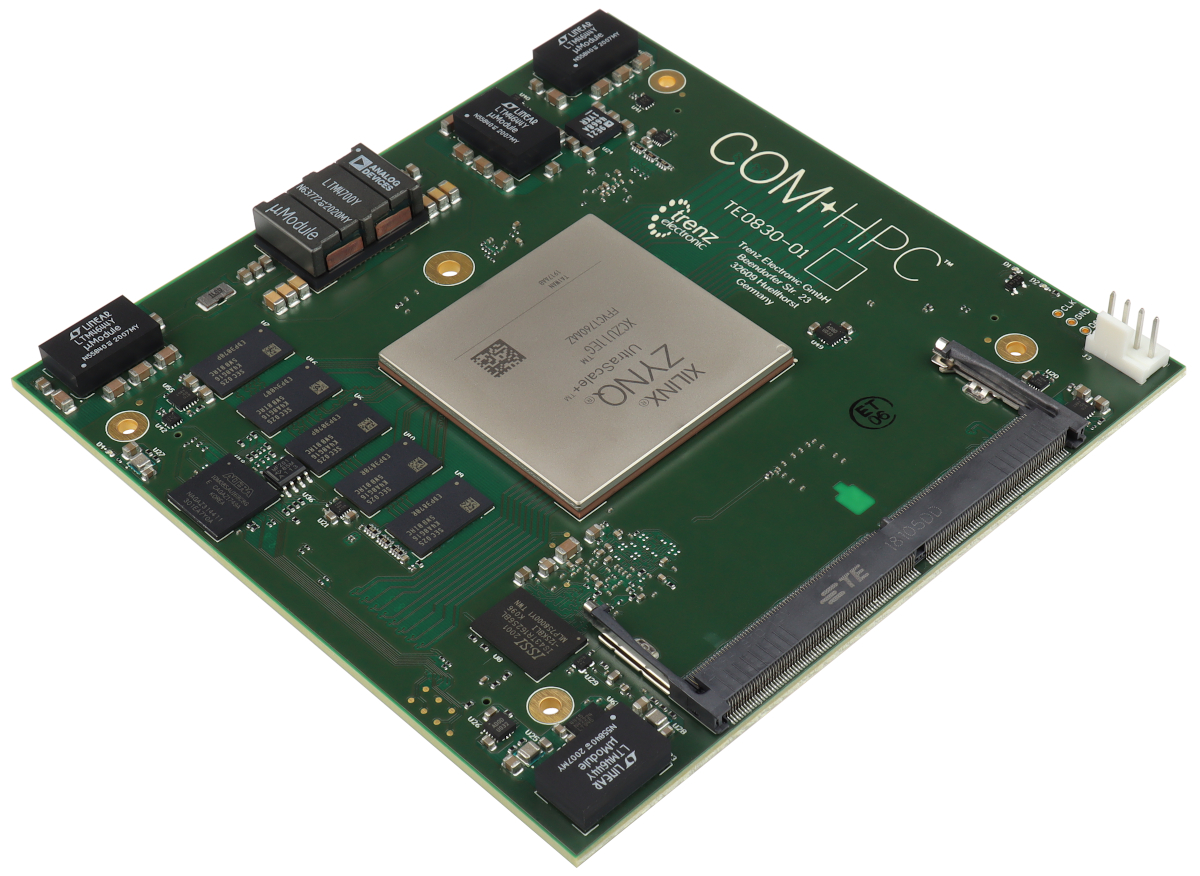

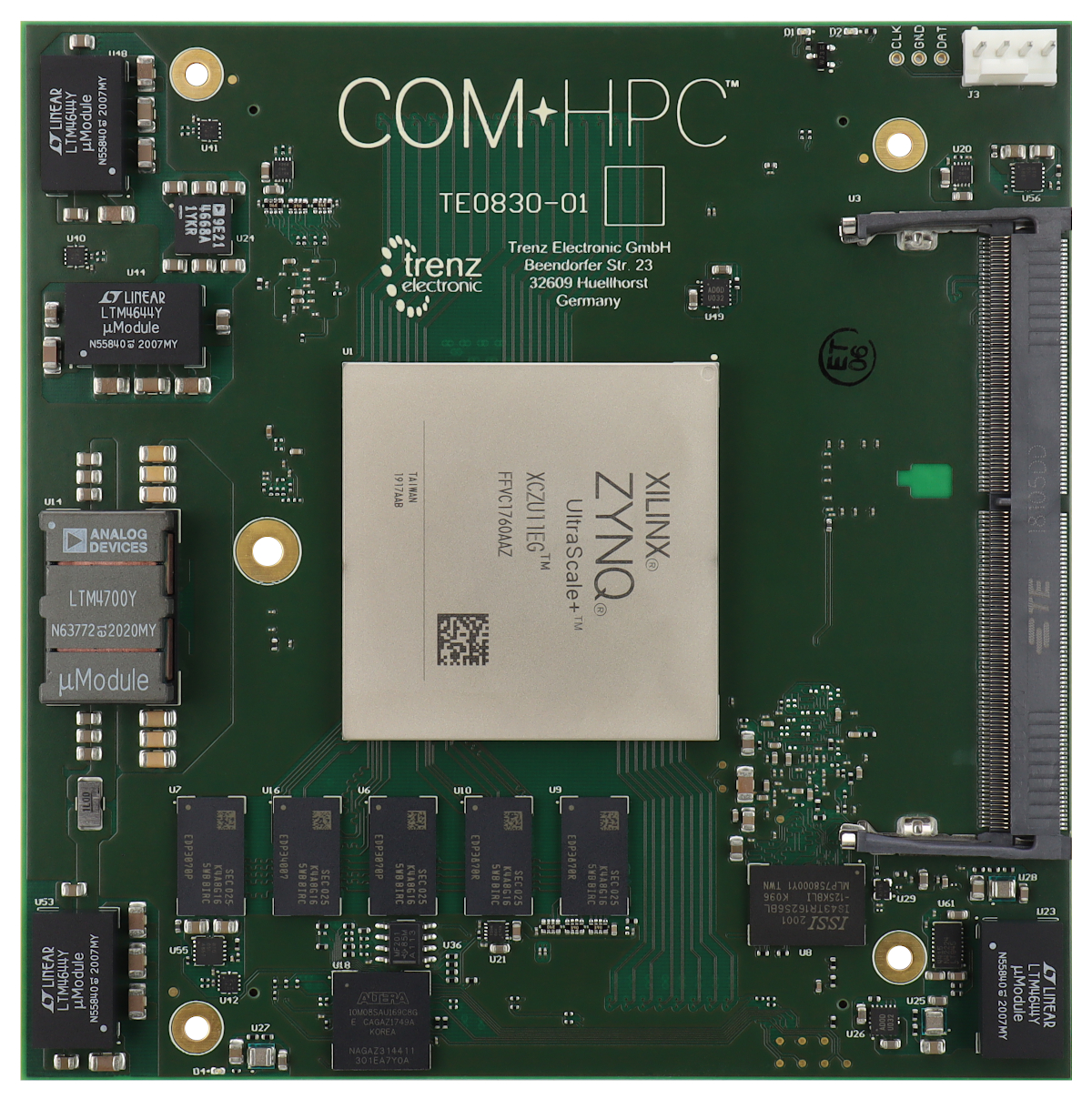

Description

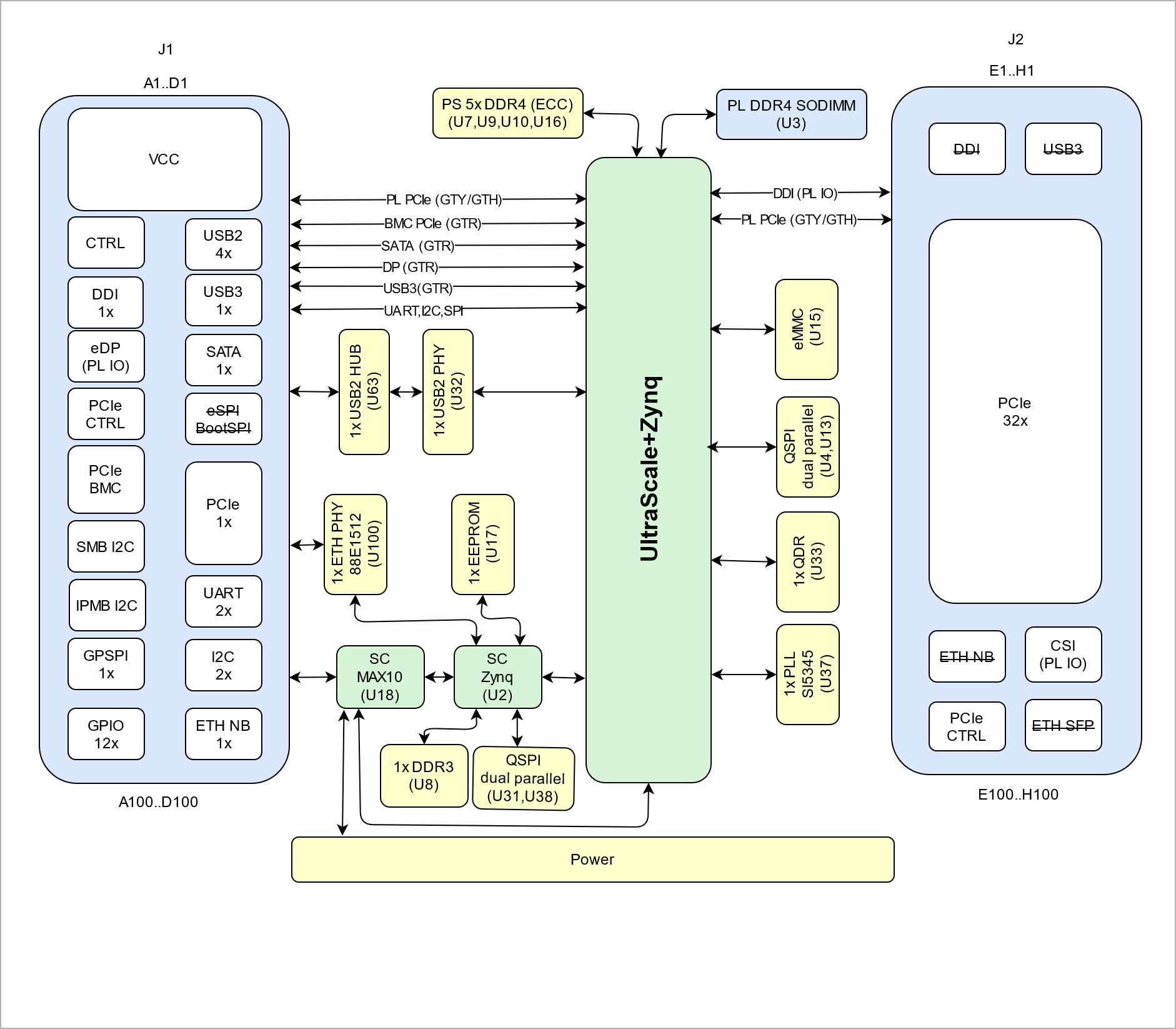

The TE0830 features high memory connectivity (PS up to 8 GByte and PL DDR up to 16 GByte) as well as fast Gigabit transceivers (up to 32.75 Gb/s), allowing PCIe Gen4 to be implemented as root complex or endpoint. Storage memory can be expanded as desired (SATA or M.2 PCIe storage card on carrier). In addition to these interfaces, USB, Gigabit Ethernet, and several other common interfaces are available. The JTAG connection for programming the ZynqMP can be done via GPIO pins or conveniently via Ethernet (with current firmware), so use in A server area is also possible. TE0830 is currently under development, but an initial prototype has been fielded, and functionality is currently being verified on the TEBT0830 test carrier.

This is the prototype configuration of TE0830, but there are still many configuration options available that you can customize to meet your specific needs.

More information will be posted to our Wiki COM-HPC SoM documentation over time.

All parts are at least industrial temperature range of -40°C to +85°C. The module operating temperature range depends on the customer’s design and cooling solution.

Key Features (preliminary)

- SoC/FPGA (AMD Zynq™ UltraScale+™)

- Package: FFVC1760

- Device: ZU11 (assembly option ZU17, ZU19 possible*)

- Engine: EG

- Speed: -1 (assembly option, -2,-3*, ** possible)

- Temperature: I (assembly option E, (Q, M) possible*,**)

- RAM/Storage

- DDR4 (PS connected)

- Data width: 72-bit with ECC

- Size: 4 GByte (assembly option up to 8 GByte possible*)

- Speed:***

- DDR4 SODIMM (PL connected)

- 72-bit DDR4 with ECC

- Size: max 16 GByte*

- Speed: NA*

- e.MMC

- Data width: 8-bit

- Size: 64 GByte (max)

- QSPI boot Flash in dual parallel mode

- Data width: 8-bit

- Size: 128 MByte (assembly up to 512 MByte possible*)

- QDDRII

- Size: 18 Mbit (assembly option possible*, default not assembled)

- MAC address serial EEPROM with EUI-48™ node identity

- DDR4 (PS connected)

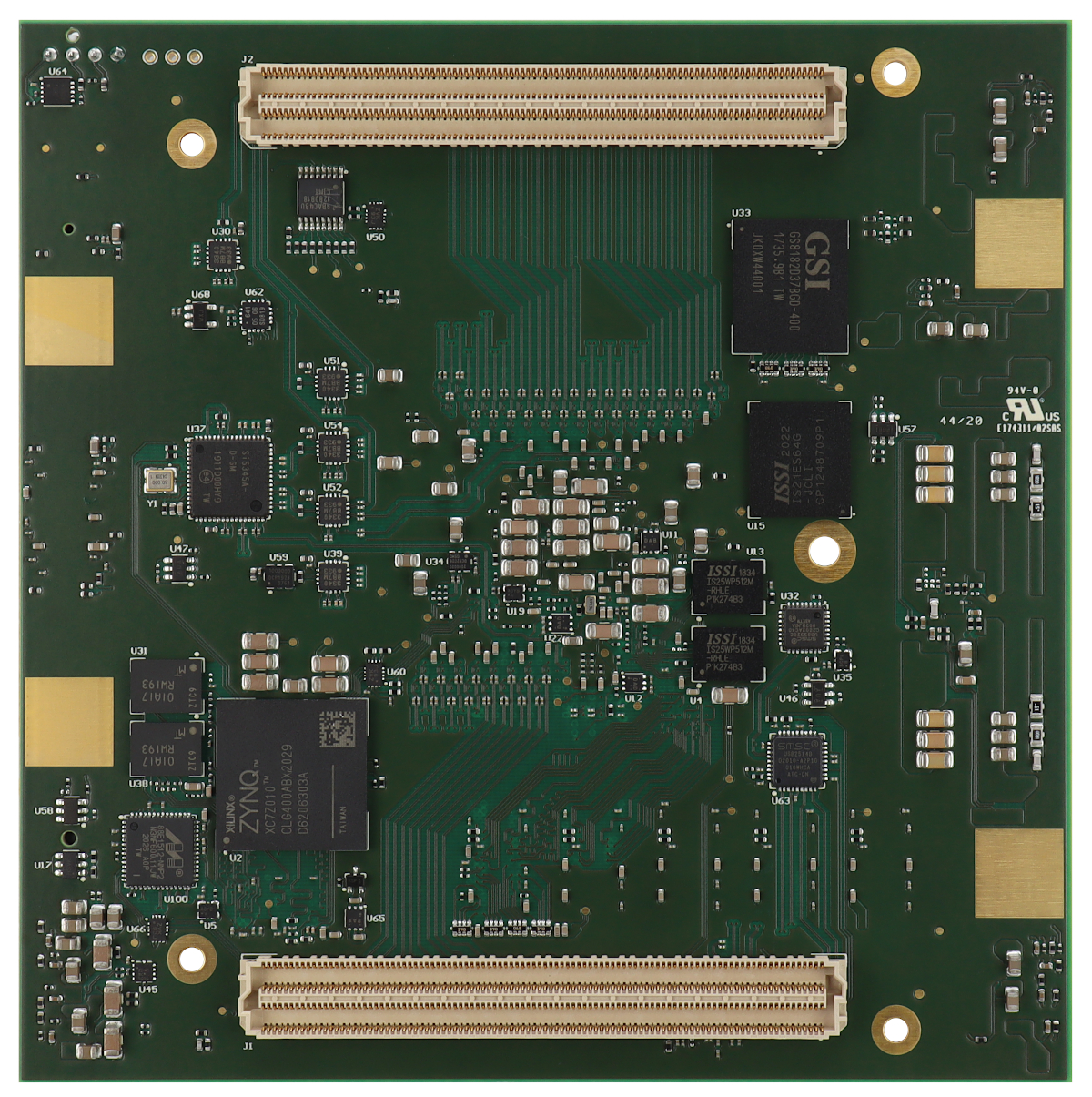

- On Board

- SC CPLD ans SoC

- Intel MAX 10: 10M08

- AMD Zynq-7000™: XC7Z010 with 128 MByte QSPI and 512 MByte DDR3 (16-bit)

- PLL SI5345

- Gigabit ETH PHY

- USB2 HUB

- USB2 PHY

- SC CPLD ans SoC

- Interface (2 x 400pin COM-HPC connectors)

- 1 x PCIe SMB (ZynqMP PS GTR)

- PCIe up to 48 lane (16 x GTY (32.75 Gb/s) and 32 x GTH (16.3 Gb/s))**

- 1 x Gbit Ethernet

- 4 x USB2

- 1 x USB3 (ZynqMP PS GTR)

- 1 x DDI (DP) (ZynqMP PS GTR)

- 1 x SATA (ZynqMP PS GTR)

- 1 x SPI

- 1 x I2C SMB

- 3 x I2C

- 2 x UART (1x ZynqMP, 1x SC Zynq)

- 12 x GPIO (JTAG over GPIO)

- PL HP IOs x32 (15 diff) over COM-HPC CSI interface

- Power

- 12V main

- 5V standby

- 2.0-3.3V RTC

- Dimension

- COM-HPC client module size B (120 x 120 mm)