Description

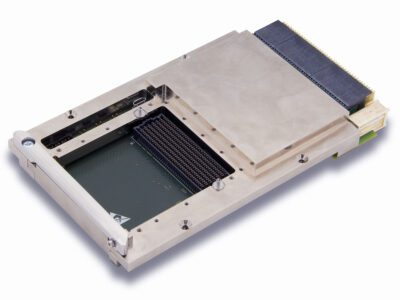

The VITA 46 11 2022 software IP core implements all requirements defined for a Tier 3 IPMC Typical target platforms of this software core are OpenVPX and SOSA aligned payload modules which interface to a Chassis Manager through the IPMB interfaces on the backplane.

The bare metal C implementation is lightweight and supports various microcontroller architectures such as ARM and RISC V Functions that make use of dedicated microcontroller peripherals are provided as part of reference designs, for example the I 2 C controller of the Microchip SAMV 71 or the PolarFire ® RISC V SoC Other microcontroller designs can be made available on request.

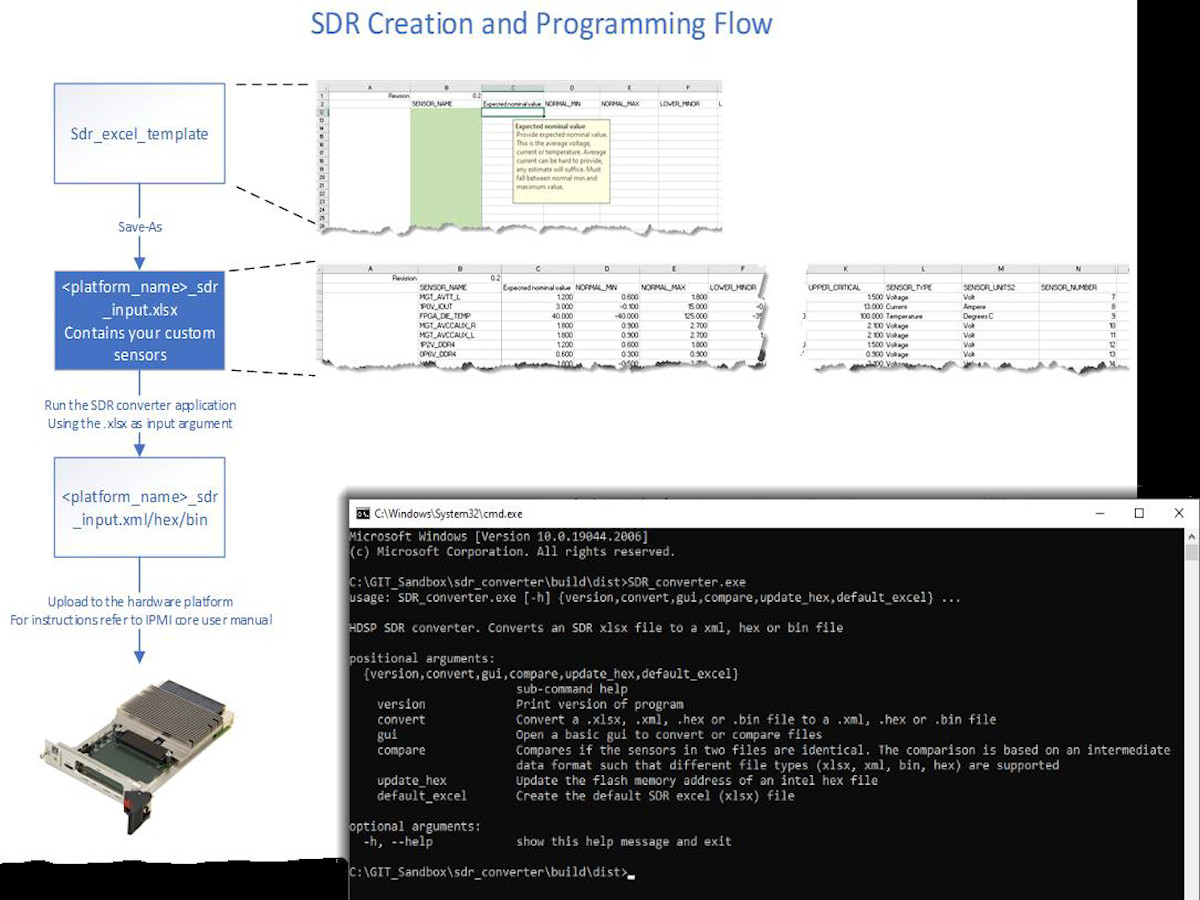

The IP core is delivered with an FRU and an SDR compiler utility The SDR compiler takes sensor values and thresholds provided by the customer using the delivered SDR excel template It generates required SDR data to be uploaded to the flash of the IPMC Different output formats are available supporting standard file formats such as hex and bin, suitable for automated programming during board production.

Hybrid DSP provides support with integration or can fully implement customers board management and IPMC functionality.

DELIVERABLES

- VITA 46.11 IPMC source code

- Reference design

- SDR converter utility with templates

- FRU compiler with templates

- Documentation

- Provided as archive via secured file transfer, or customer facing private GIT repository for optimized version control (Clone, Fetch, Pull, Push)

REFERENCE DESIGNS

- Default reference designs available for:

- Microchip ATSAMV71-XULT, ARM

- Microchip MPFS-ICICLE-KIT-ES, RISC V

- Command Line Interface (CLI) through UART

- Redundant IPMB connection to Chassis Manager

- Chassis Manager to be provided by customer

- GA and NVMRO pin settings can be configured through CLI

- Threshold sensor values can be emulated through CLI to test event generation

- Quick Start Guide providing instructions to connect to Chassis Manager and get started with the software

- Ipmitool docker image with example use cases

- Custom BMC and IPMI reference and production designs available on request

SDR AND FRU UTILITIES

- SDR Spreadsheet .xlsx template permits addition of custom sensors without in-depth VITA 46.11 knowledge

- FRU .xml template to generate the minimum FRU data required by VITA 46.11

- Command line SDR and FRU converter generating .bin or Intel .hex files that can be uploaded through the standard IDE programming interfaces or a customer-specific interface

- SDR and FRU compilers delivered as Windows Executables

A readily maintainable and customizable BMC implementation with VITA 46.11 Tier 3 support for 3rd party board developments

A readily maintainable and customizable BMC implementation with VITA 46.11 Tier 3 support for 3rd party board developments