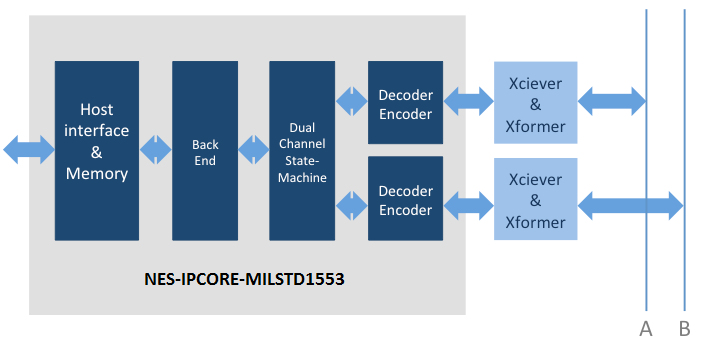

Description

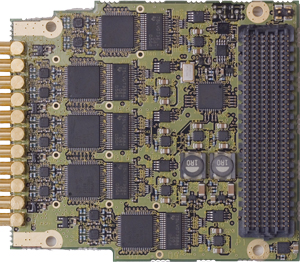

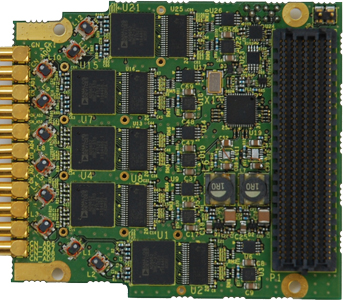

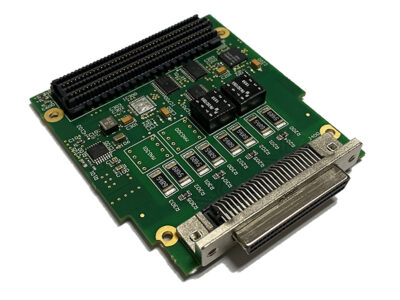

Combining the benefits of programmable devices ( and Nolam Embedded systems IP Cores provides a small size, robust, reliable, flexible, future proof and cost-effective solution for Mil Std 1553 interface.

Nolam Embedded systems IP cores are designed for any requirement and application Customers can choose between various configurations and interfaces.

The NES IPCORE M 1553 is designed for simple applications, where no CPU is controlling the system, to the most complex implementations, where a Local Bus is used by the CPU or Axi bus.

The NES IPCORE M 1553 is available and works with any FPGA, clock frequency and 1553 transceiver, providing the most robust, yet flexible, solution.

Compatibility:

- MIL STD 1553

- MIL STD 1553 B Notice 2 and 1760

- RT Validated according to the test plan from MIL HDBK 1553 A

- 1 Mbps Date Rate

- Connects to any transceiver,Transformer pair

RAM :

- 4,8,16,32,64K by 16 bits Dual port

- RAM (Limited by FPGA resources only)

Clock:

- Any Even frequency from 12Mhz and higher 100Mhz

- Including 33Mhz for PCI and 125Mhz for PCI Express implementations

Supported FPGA:

- Any FPGA with sufficient number of LUTs and dual port memory

- FPGA families from the following vendors Xilinx (AMD),Altera (Intel),Lattice Achronix Efinix ,Microchip Quicklogic

Deliverables:

- Net list for the desired core (BC/RT/ for FPGA family and memory

- User’s Manual

- Sample VHDL code that incorporates Synthesis script for sample code

The NES IPCORE M1553 is suitable for simple 1553 applications, protocol translators and hardware based implementations. NES IPCORE M1553 is suitable for more complex 1553 implementations, where the application is controlled by software