Description

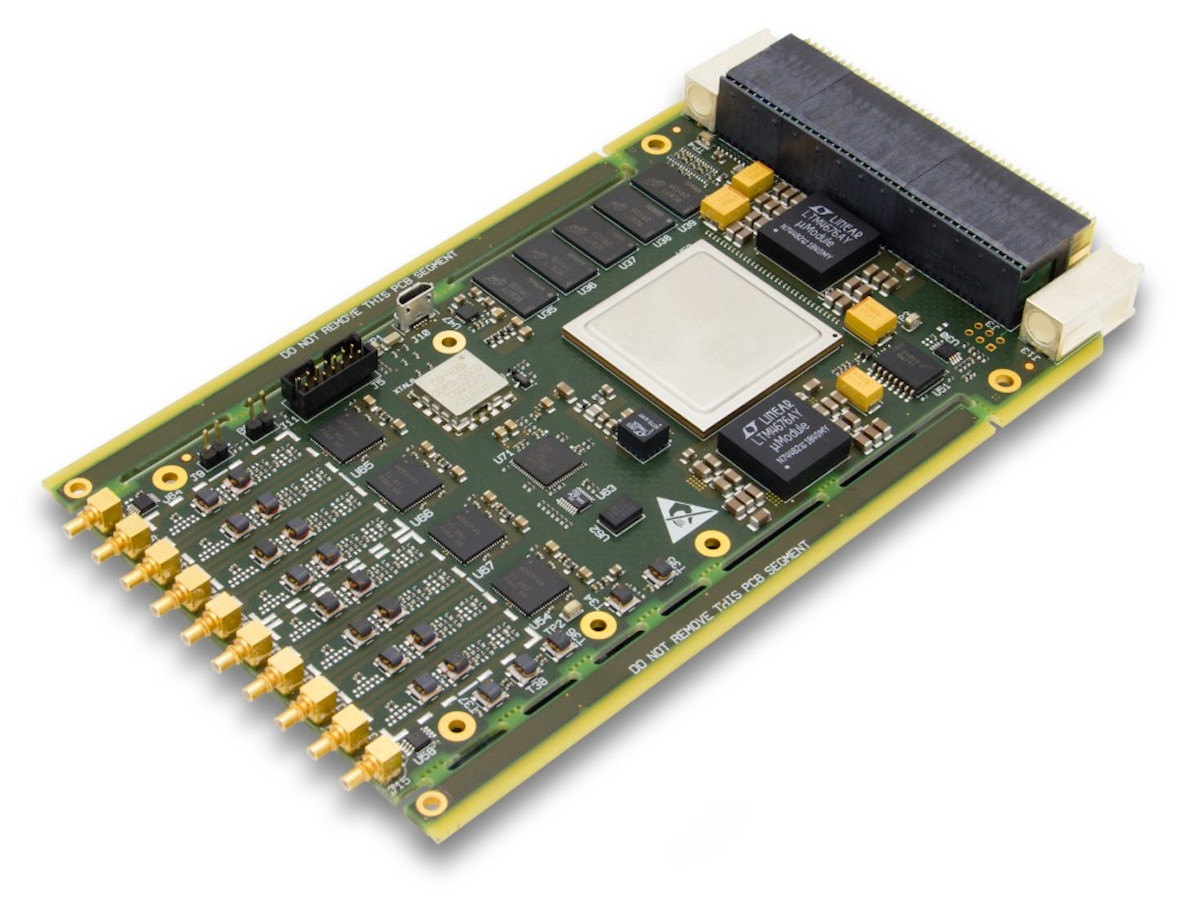

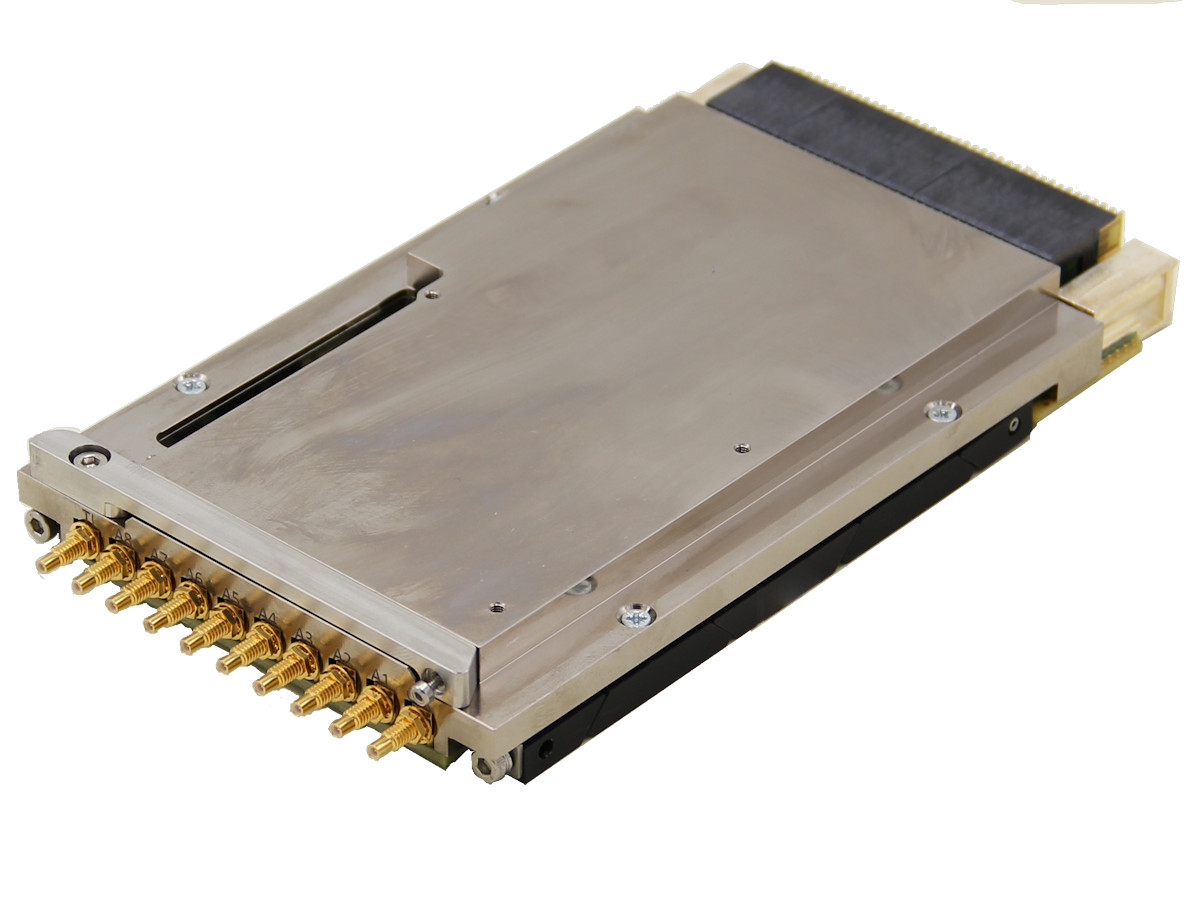

The 3U V3UADC01P is a member of Hybrid DSP’s XU01P 1156 Core Series of mid-range, cost-effective, rugged processing boards based on the AMD Kintex UltraScale A1156 FPGA package, up to 8GB DDR4 and an ARM-based Board Management Controller (BMC).

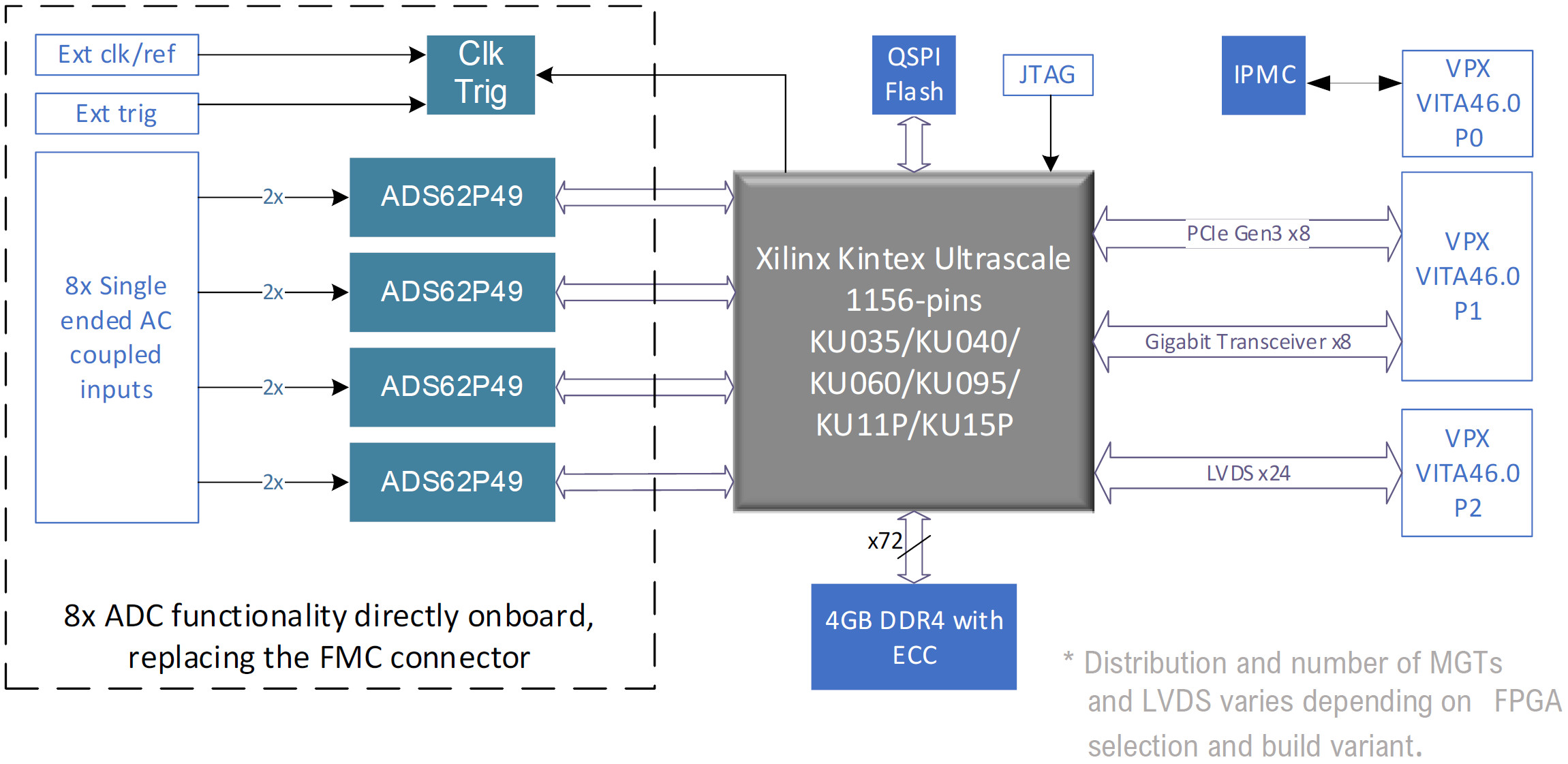

The V3UADC01P is available with a range of build options for OpenVPX air and conduction-cooled-based systems as well as those aligned with the SOSA Technical Standard. Features include eight ADC channels running at up to 250Msps with coax on either the front panel or optionally VITA 67 coax blind mate connectors on the backplane. The board supports external and internal trigger and clock sources.

In addition to numerous standard build options, the design is optimized for rapid customization of many key features, including the type of coax connectors, front panel design, cooling solution, reference firmware, and BMC.

The monolithic V3UADC01P is based on the V3UFMC01P and a customer’s legacy FMC ADC module. Hybrid DSP’s Modified-COTS optimized base XU01P design permitted a lowrisk, rapid form-fit-function replacement of the existing modular solution leading to simplification of supply-chain, lifecycle management and serviceability, as well as a significant cost-saving across the program lifetime.

What’s Included?

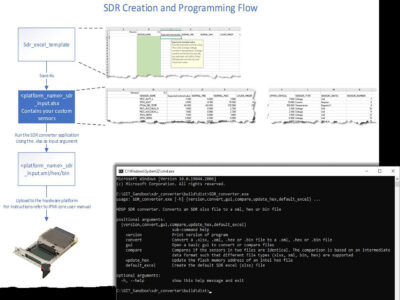

- Python API and reference application

- VHDL based reference design

- Vivado reference project

AMD UltraScale 8CH ADC

AMD UltraScale 8CH ADC