Description

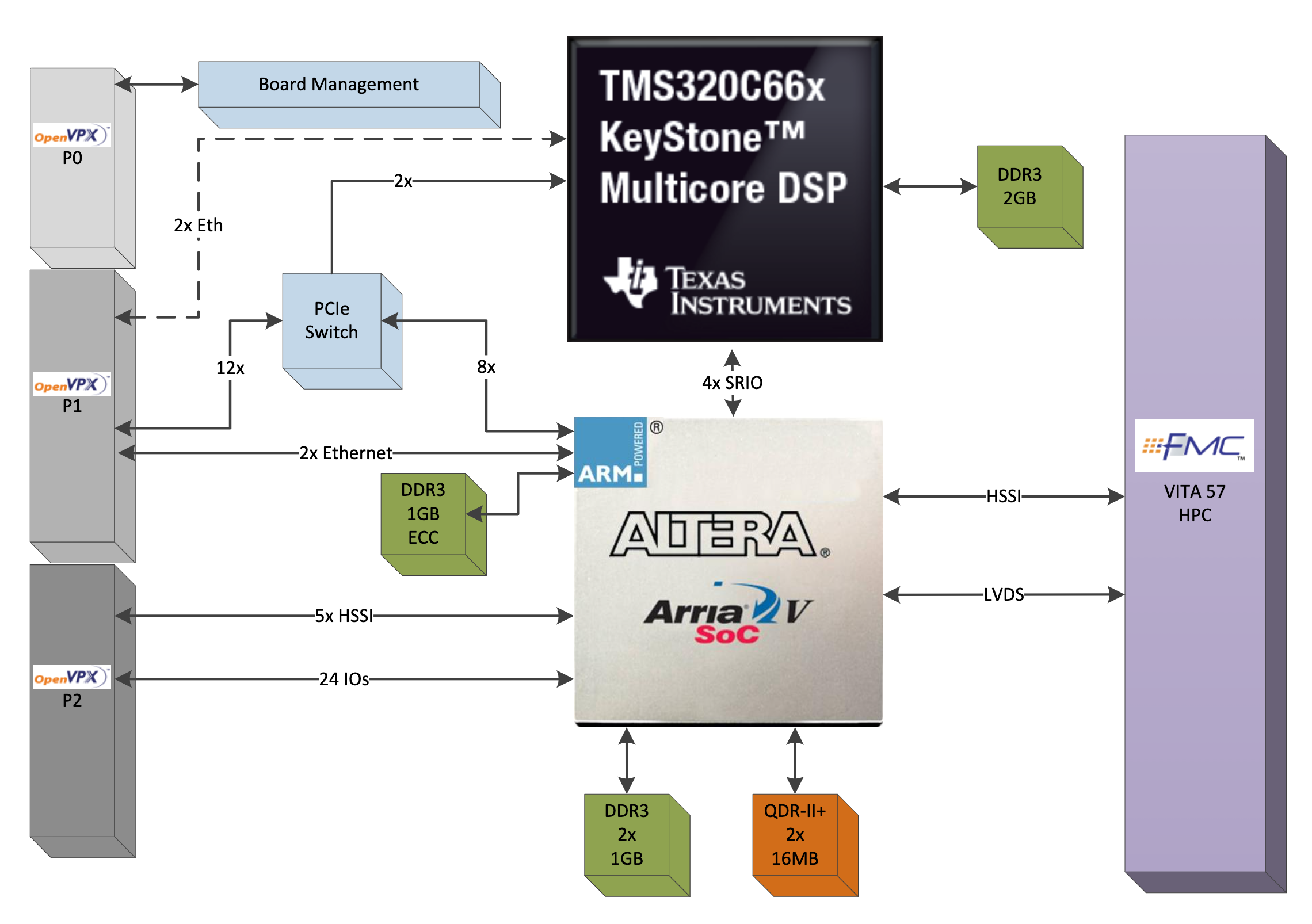

The VF361 is a 3U OpenVPX module that leverages on the ALTERA Arria ® V SoC FPGA, ARM Cortex-A9, and Texas Instruments Keystone Multicore DSP technology to provide a high bandwidth processing platform, ideally suited for computation and bandwidth intensive applications such as RADAR, networking, SIGINT, EW, SDR and Video.

The Arria® C SiC FPGA integrates a Hard Processor System (HPS) with dual-core ARM Cortex-A9 MPCore processor, DDR SDRAM controller, Memory Management Unit (MMU) and numerous interface peripherals into the FPGA.

The ARM Neon ™ media processing engine with double-precision vector floating-point (VFP) unit accelerates multimedia and signal processing algorithms.

The ARM processor supports symmetric (SMP) and asymmetric (AMP) multiprocessing, running from simple bare-metal applications to single and multicore operating systems like Linux, VxWorks® and other. It is ideal for safety and mission critical software applications.

The ARM Development studio (DS-5) Altera Edition provides a suite of tools for embedded C/C++ software development with powerful debugging capabilities such as cross-trigger (FPGA <-> ARM) debug, program trace and multi-core debug through the ARM Coresight™ JTAG debug port.

A PC based Altera SoC virtual target allows firmware and software development to start on a virtualised Altrea development board.

SoC FPGA:

- Arria® V SX family on the KF40 (1517 FBGA) package

- SX Device variants: B3 and B5

- Hard Processor System (HPS)

- Embedded device memory: 19-25 Mb

- Embedded device multipliers (18×18)L 1618 – 2180

- DDR3 ARM external Memory

- Up to 1GB DDR3 @ 667MHz, default 512Mb

- DDR3 and QDRII+ FPGA external memory

- Up to 1GB DDR3 @ 667 MHz (arranged as 256M x 32-bit), default 512MB

- Up to 16MB QDRII+ SRAM @ 400MHz (arranged as 8M x 18-bit), default 8MB

Hard Processing System (HPS)

- Dual-Core ARM Cortex-A9 MPCore processor

- ARM Neon™ media processing engine with double precision vector floating point (VFP)

- 8-channel DMA controller

- USB On-The-Go controller (OTG)

- Numerous other system and interface peripherals

- ARM Coresight™ JTAG debug access port

Digital Signal Processing:

- TI KeyStone Multicore C667x family of processors

- Up to 8 cores @ 1.2 GHz

- External memory: Up to 2Gb DDR3 @667MHz, default 1GB

FPGA Mezzanine Card (FMC-HPC):

- 5x High-Speed Serial Interface lanes

- Differential and single-ended interfaces on LA and HA

VPX Interface:

- Complies with OpenVPX MOD3-PAY-3F2U-16.2.12-2 module profile

- PCIe Gen2 Data plane (3x Fat Pipes)

- GigE 1000BASE-BX Control plane (2x Ultra-Thin Pipes)

- Payload module with System Controller capability

- Supports FPGA configurable User I/O on P2

- 24x single-ended 2.5V LVCMOS I/Os

- 10x High-Speed Serial Interface lanes