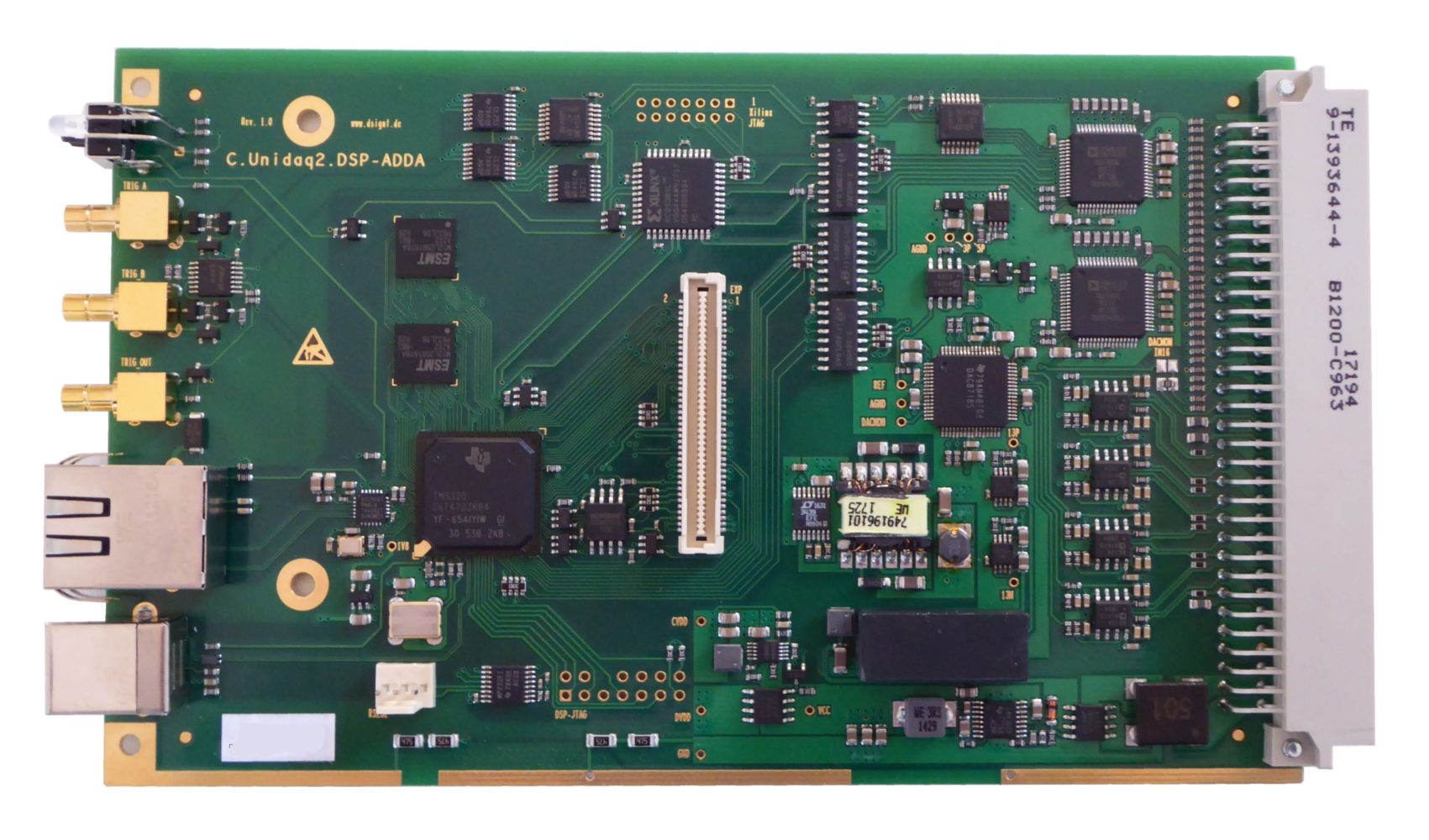

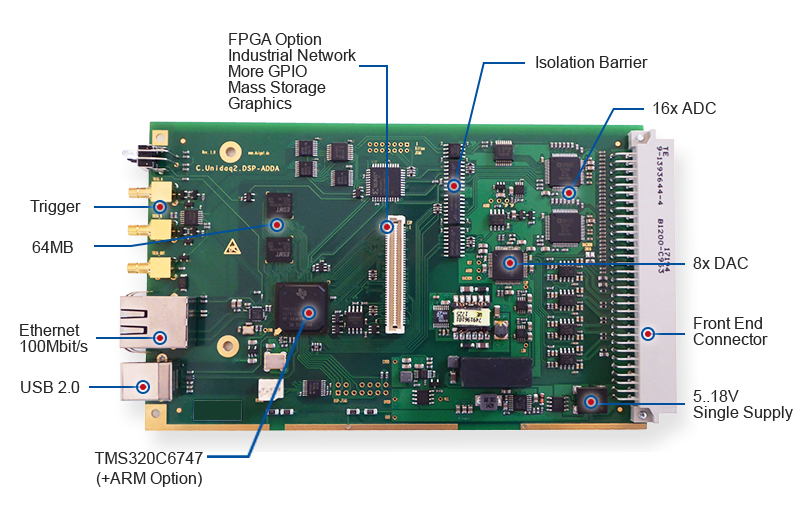

Description

Application Areas

- vibration analysis and machine monitoring

- acoustic measurements, microphone array processing

- servo control and positioning systems

- measuring devices for research, development, and test stands

- laboratory equipment for education classrooms

Key Features

- 16 simultaneously sampling SAR A/D converters, 16-bit, 175kS/s

- 8 inherent monotonic D/A converters, 16-bit, 105kS/s

- internal or external sampling triggers for ADC and DAC

- 456 MHz floating-point DSP (TMS320C6747) with 64 Mbytes SDRAM

- USB2.0 Device Port and 100Base-T Fast Ethernet

- expansion port for mass storage, fieldbusses, display, GPIO, FPGA, etc.

- isolation barrier between analog and digital circuits

- single-supply power 5-18V, typ. 3W